# Development and Certification of Dependable Mixed-Criticality Embedded Systems

DISSERTATION

zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften

> vorgelegt von Dipl.-Ing. Asier Larrucea Ortube

> Promotionskommission: Prof. Dr. Roman Obermaisser Prof. Dr. Alfons Crespo Prof. Dr. Christoph Ruland Prof. Dr. Kristof Van Laerhoven

eingereicht bei der Naturwissenschaftlich-Technischen Fakultät der Universität Siegen Siegen 2017

Tag der mündlichen Prüfung: 06 July 2017

## **Declaration of Authorship**

I, Asier Larrucea Ortube, declare that this thesis titled, 'Development and Certification of Dependable Mixed-Criticality Embedded Systems' and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all main sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

#### UNIVERSITÄT SIEGEN

### Zusammenfassung

#### Entwicklung und Zertifizierung von zuverlässigen eingebetteten Mixed-Criticality-Systemen

von Asier LARRUCEA ORTUBE

Der Übergang von herkömmlichen Verbundarchitekturen zu integrierten Architekturen ermöglicht die Integration von Funktionalitäten mit unterschiedlichen Kritikalitäten in Bezug auf die Betriebs- und Angriffssicherheit sowie Echtzeit fähigkeit in einer einzigen eingebetteten Computer-Plattform. Der Trend zu Multi-core- und Many-Core-Architekturen hat des Weiteren zu dieser Tendenz beigetragen, indem er Vorteile in Hinblick auf die Kosten, Größe und Gewicht liefert. Multi-Core-Architekturen sind derart gestaltet, dass eine maximale durchschnittliche Leistung auf Kosten einer erhöhten Komplexität und Wechselwirkungen zwischen Applikationen geboten wird. Partitionierungslösungen wie Hypervisoren (z.B. XtratuM, PikeOS) werden normalerweise zur Bewältigung von mit diesen Architekturen in Verbindung stehenden Herausforderungen verwendet. Sie begrenzen die Auswirkung von Veränderungen und Störungen auf abgesteckte Bereiche des Systems, auch Partitionen genannt, ermöglichen die Wiederverwendbarkeit und verringern die Komplexität. Derartige Partitionen können individuell und mit unterschiedlichen Kritikalitätslevels gestaltet, entwickelt und zertifiziert werden (z.B. Sicherheitsintegritätslevel (SIL) 1 bis 4 gemäß IEC 61508). Obgleich auch partitionierte Multi-Core-Architekturen die o.g. Vorteile aufweisen können sie viele Probleme im Zusammenhang mit der Zertifizierung mit sich bringen, wie z.B. die Bewertung der zeitlichen Unabhängigkeit, was wiederum zu einer beachtlichen Erhöhung der Engineeringund Zertifizierungskosten führt. Darüber hinaus kann ein eingebettetes System verteilte Subsysteme mit Kommunikationsnetzwerken (wie z.B. EtherCAT) erforderlich machen, um den Rechnerressourcenbedarf zu decken, Fehlertoleranz sicherzustellen und die Installationsanforderungen zu erfüllen. Der allgemeine Trend hin zur Integration von Funktionalitäten mit unterschiedlichen Kritikalitäten in einer einzigen eingebetteten Computer-Plattform erfordert die Implementierung von sicheren und vorhersagbaren Kommunikationssystemen mit einer zeitlichen Trennung zwischen den verschiedenen Kritikalitäten. Aus diesem Grund stellen sich für Kommunikationsnetzwerke besondere Herausforderungen in Hinblick auf die Zertifizierung, wie z.B. ein Sicherstellen der Non-Interference zwischen sicherheitskritischen und nicht sicherheitskritischen Kommunikationsaktivitäten. In dieser Dissertation werden modulare Sicherheitskonzepte für einen IEC 61508-konformen generischen Hypervisor, die Partition, kommerzielle Mehrkernprozessoren und Netzwerke mit gemischter Kritikalität vorgestellt. In einem modularen Sicherheitsnachweis werden sicherheitsrelevante Argumente und Nachweise definiert, die ein System aufweisen muss, um die Sicherheitsstandards zu erfüllen. Die in dieser Dissertation definierten Sicherheitsnachweise sind von einer Zertifizierungsstelle im Rahmen des Europäischen Forschungsprojekts DREAMS bewertet worden. Darüber hinaus wird in dieser Doktorarbeit eine Verbindungsanalyse für kommerzielle Technologien, wie z.B. den XtratuM-Hypervisor, Zynq-7000, TTEthernet und EtherCAT-Netzwerke durchgeführt. In dieser Analyse wird beschrieben, inwiefern ein kommerzielles System in generischen modularen Sicherheitsnachweisen identifizierte sicherheitsrelevante Anforderungen erfüllt.

Als Ergebnis der Definition von modularen Sicherheitsnachweisen und der dazugehörigen Analyse des IEC 61508 Sicherheitsstandards sind jene Komponenten identifiziert worden, die Herausforderungen für die Entwicklung und Zertifizierung von derzeit vorhandenen eingebetteten Computer-Plattformen mit gemischter Kritikalität aufweisen. Außerdem konnte festgestellt werden, dass die durch den Sicherheitsstandard IEC 61508 empfohlenen Maßnahmen und Diagnosetechniken meist auf Single-Core-Architekturen ausgerichtet sind, bei denen eine Ressource lediglich mit einer Komponente geteilt werden kann. Diese Maßnahmen und Diagnosetechniken sind keineswegs auf heute verfügbare Systeme mit gemischter Kritikalität anwendbar, da bei ihnen sehr häufig eine Ressource mit mehr als einer Komponente geteilt wird. So kann z.B. bei einer Multi-Core-Architektur gleichzeitig mehr als eine Komponente auf einen Speicherbereich zugreifen, was wiederum zu Wechselwirkungen führt, die die Sicherheit des Systems gefährden können. In dem Bestreben, eine Antwort auf diese Herausforderungen zu finden, werden in dieser Dissertation verschiedene allgemeine domänenübergreifende Modelle und Lösungen für bei der Entwicklung von Systemen mit gemischter Kritikalität häufig auftretende Probleme vorgestellt. Diese Modelle werden ausgehend vom DREAMS-Architekturstil untersucht, definiert und letztlich in einer Fallstudie zu einer Windkraftanlage implementiert. Diese Fallstudie liefert ein realistisches Systemszenario, in das die in dieser Dissertation aufgeführten Lösungen integriert und letztlich bewertet werden können.

#### UNIVERSITY OF SIEGEN

### Abstract

#### Development and Certification of Dependable Mixed-Criticality Embedded Computing Systems

by Asier LARRUCEA ORTUBE

The transition from conventional federated architectures to integrated architectures enables the integration of functionalities with different criticality concerning safety, security and real-time on a single embedded computing platform. The trend towards multi-core and many-core architectures has further contributed to this tendency, providing benefits regarding cost-size-weight. Multi-core architectures are designed for offering the maximum average performance at the cost of increasing complexity and interferences. Partitioning solutions such as hypervisors (e.g., XtratuM, PikeOS) are commonly used to tackle the challenges related to these architectures. They limit the impact of changes and faults to reduced areas of the system, also called partitions, enabling reusability and reducing the complexity. Partitions can be designed, developed and certified individually with different levels of criticality (e.g., Safety Integrity Level (SIL) 1 to 4 according to IEC 61508). However, although partitioned multi-core architectures provide the benefits mentioned before, they imply many challenges to certification such as the assessment of the temporal independence, which leads to a significant increase in the engineering and certification cost. Furthermore, an embedded system may require distributed subsystems with communication networks (such as EtherCAT) to satisfy the computational resource demands, ensure fault-tolerance and satisfy the installation requirements. The broad trend of the integration of functionalities with different criticality on a single embedded computing platform involves the implementation of safe and predictable communication systems with temporal segregation between different criticality. Therefore, communication networks represent certification challenges such as guaranteeing the non-interference between safety-critical and non safety-critical communications. This dissertation presents the modular safety concepts for an IEC 61508 compliant generic hypervisor, partition, commercial-off-the-shelf (COTS) multi-core device and mixed-criticality network. A modular safety case (MSC) defines the safety-related arguments and evidences that a

system must fulfil in order to be compliant with a safety standard. The MSCs defined throughout this thesis have been assessed by a certification body within the context of the European research project DREAMS. Besides, this dissertation defines the linking analysis for commercial technologies such as XtratuM hypervisor, Zynq-7000 multi-core device and TTEthernet and EtherCAT networks. A linking analysis describes the way in which a commercial system fulfils the safety-related requirements identified in the generic modular safety cases.

As a result of the definition of the modular safety cases and associated analysis of the IEC 61508 safety standard, the remarkable components that imply challenges in the development and certification of today's mixed-criticality embedded computing platforms have been identified. In addition, it is detected that the measures and diagnostic techniques recommended by the IEC 61508 safety standard are mostly geared to singlecore architectures where a resource cannot be shared among more than one component. These measures and diagnostic techniques are not at all applicable to today's mixedcriticality systems where sharing a resource among more than one component is a common task. For example, in multi-core architectures a memory area can be accessed simultaneously by more than one component (e.g., CPUs), leading to interferences that may jeopardise the safety of the system. In order to give a solution to those challenges, the dissertation presents several generic cross-domain patterns for commonly occurring problems in the development of mixed-critical systems. These patterns are analysed, defined and implemented in a wind turbine case study based on the DREAMS architecture style. This case study provides a realistic system scenario where the solutions generated in this dissertation are integrated and evaluated.

### Acknowledgements

This thesis has been carried out in collaboration with the Electronic department of IK4-Ikerlan research centre (Basque Country, Spain) and Embedded Systems department of University of Siegen (Siegen, Germany).

I would like to thank Prof. Roman Obermaisser for his support during these three years. I really appreciate the time that he has dedicated to discuss the state of my thesis and guide me through the right way. In addition, I would like to thank Dr. Jon Perez for giving me the opportunity to do a PhD under his direction on the topic of safety mixed-critical embedded computing platforms between IK4-Ikerlan and the University of Siegen.

Many thanks to my colleagues from IK4-Ikerlan for enduring me and cheer me up whenever I have needed. Many thanks also to my colleges in the University of Siegen for their hospitality and support during my stages in Germany, you make me feel at home.

I also want to thank the partners with who I have worked in the European research project DREAMS for their support and cooperation.

Last but not least, I heartily thank the compression received from my parents, brother, family and friends. You have patiently endured my frustrations and moodiness during the last three years and more.

# Contents

| De            | eclara                                                                           | ation of Authorship                                                               | i                                                                     |

|---------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Zι            | ısam                                                                             | menfassung                                                                        | iii                                                                   |

| A             | ostra                                                                            | $\mathbf{ct}$                                                                     | v                                                                     |

| A             | cknov                                                                            | wledgements                                                                       | vii                                                                   |

| Co            | onten                                                                            | ıts                                                                               | viii                                                                  |

| $\mathbf{Li}$ | st of                                                                            | Figures                                                                           | xiii                                                                  |

| $\mathbf{Li}$ | st of                                                                            | Tables                                                                            | xvii                                                                  |

| 1             | <b>Intr</b><br>1.1<br>1.2<br>1.3                                                 | oduction         Objective         Contributions         Structure of this Thesis | <b>1</b><br>3<br>4<br>4                                               |

| 2             | $2.1 \\ 2.2 \\ 2.3 \\ 2.4 \\ 2.5 \\ 2.6 \\ 2.7 \\ 2.8 \\ 2.9 \\ 2.10 \\ 2.11 \\$ | kgroundMixed Criticality Systems                                                  | 7<br>8<br>8<br>9<br>9<br>10<br>11<br>13<br>13<br>14<br>14<br>15<br>16 |

| 3             | Stat<br>3.1                                                                      | The Art         Modularity among Standards         3.1.1         IEC 61508        | <b>19</b><br>19<br>19                                                 |

|          |                | 3.1.2          | ISO 26262                                                         | 20              |

|----------|----------------|----------------|-------------------------------------------------------------------|-----------------|

|          |                | 3.1.3          | EN 50129                                                          | 22              |

|          |                | 3.1.4          | DO-178 Integrated Modular Avionics (IMA)                          | 24              |

|          | 3.2            | Modul          | lar Safety Case Notation Languages                                | 25              |

|          |                | 3.2.1          |                                                                   | 26              |

|          |                | 3.2.2          |                                                                   | 28              |

|          |                | 3.2.3          |                                                                   | 29              |

|          |                |                |                                                                   |                 |

| <b>4</b> | $\mathbf{DR}$  | EAMS           | Architecture Style                                                | <b>31</b>       |

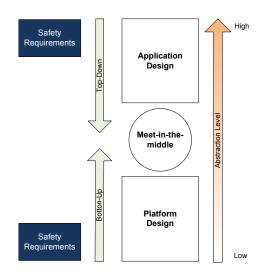

|          | 4.1            | Safety         | Development Process for Mixed-Criticality Systems                 | 33              |

|          |                | 4.1.1          | Meet-in-the-Middle Methodology                                    | 36              |

|          |                | 4.1.2          | Traceability                                                      | 38              |

|          |                | 4.1.3          | Modularity                                                        | 38              |

| 5        | Мо             | dular 9        | Safety Cases                                                      | 41              |

| 9        | 5.1            |                |                                                                   | <b>41</b><br>42 |

|          | $5.1 \\ 5.2$   |                | dular Safety Case for an IEC 61508 compliant Generic Typervisor . |                 |

|          | 5.2            |                | dular Safety Case for an IEC 61508 compliant Generic COTS multi-  | 41              |

|          | 0.0            | core de        | · ·                                                               | 49              |

|          | 5.4            |                | dular Safety Case for an IEC 61508 compliant Generic Mixed-       | чJ              |

|          | 0.1            |                |                                                                   | 54              |

|          |                |                |                                                                   |                 |

| 6        | $\mathbf{Cro}$ | oss-Don        | nain Mixed-Criticality Patterns                                   | 59              |

|          | 6.1            | Hyper          | visor                                                             | 60              |

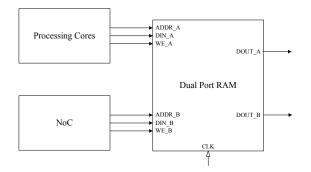

|          |                | 6.1.1          | NoC-Accessible Memory Area Diagnosis Pattern                      | 60              |

|          |                | 6.1.2          | Critical Partition Diagnosis Pattern                              | 61              |

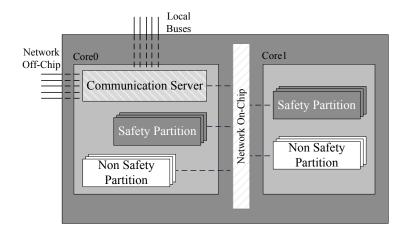

|          |                | 6.1.3          | Communication Input/Output Server Pattern                         | 63              |

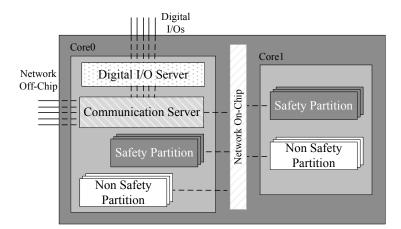

|          |                | 6.1.4          | Digital Input/Output Server Pattern                               | 63              |

|          | 6.2            | COTS           | Multi-Core Device                                                 | 65              |

|          |                | 6.2.1          | Shared Memory Diagnosis Pattern                                   | 67              |

|          |                | 6.2.2          | Cache Coherency Management Diagnosis Pattern                      | 75              |

|          |                | 6.2.3          | Inter-Connection Management Unit Diagnosis Pattern                | 78              |

|          |                | 6.2.4          | Interrupt Controller Diagnosis Pattern                            | 81              |

|          | 6.3            | Mixed          | -Criticality Network                                              | 83              |

|          |                | 6.3.1          | Network-on-Chip Diagnosis Pattern                                 | 83              |

| 7        | Cas            | se Stud        | y – Wind Turbine                                                  | 87              |

| •        | 7.1            |                | •                                                                 | 88              |

|          | 7.2            | ě              |                                                                   | 88              |

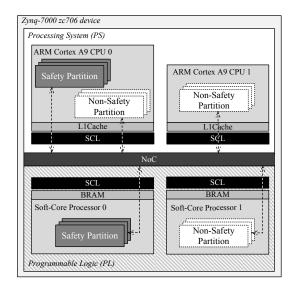

|          |                | 7.2.1          |                                                                   | 90              |

|          |                | 7.2.1          |                                                                   | 95              |

|          |                | 7.2.2          |                                                                   | 96              |

|          |                | 7.2.3<br>7.2.4 | Mixed-Criticality Networks – Linking Analysis                     |                 |

|          |                | 1.4.4          | 7.2.4.1 EtherCAT – Linking analysis                               |                 |

|          |                |                | 7.2.4.1 EtherCAT – Linking analysis                               |                 |

|          | 7.3            | System         | n of System, Product Line and Modularity                          |                 |

|          | 7.3<br>7.4     | 0              | Domain Patterns                                                   |                 |

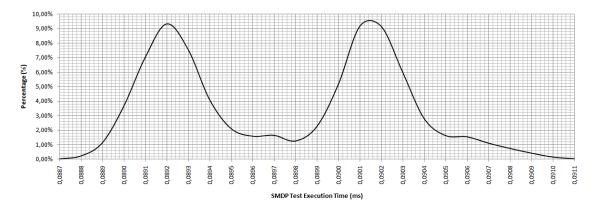

|          | 1.4            | 7.4.1          | Shared Memory Diagnosis Pattern (SMDP)                            |                 |

|          |                | 1.4.1          | Shared memory Diagnosis rational (Simple)                         | .4J             |

|   |     | 7.4.2   | Cohe   | renc | уМ | lan | age | m | en | tΙ | Jn | nit | Di | ag | gno | si | s I | Pa | tte | rn | (0 | CN | ſU | D | P) | ) | <br>• | . 134 | 1 |

|---|-----|---------|--------|------|----|-----|-----|---|----|----|----|-----|----|----|-----|----|-----|----|-----|----|----|----|----|---|----|---|-------|-------|---|

| 8 | Cor | nclusio | ns     |      |    |     |     |   |    |    |    |     |    |    |     |    |     |    |     |    |    |    |    |   |    |   |       | 143   | 3 |

|   | 8.1 | Review  | v      |      |    |     |     |   |    |    |    |     |    |    |     |    |     |    |     |    |    |    |    |   |    |   |       | . 143 | 3 |

|   | 8.2 | Future  | e work |      |    |     |     |   |    |    |    |     |    |    |     |    |     |    |     |    |    |    |    |   |    |   |       | . 144 | 1 |

#### Appendices

#### 157

| Α | Zyn           | q-7000 | COTS multi-core device –                 |     |

|---|---------------|--------|------------------------------------------|-----|

|   | $\mathbf{FM}$ | ĒA/FN  | /IECA/FMEDAs                             | 159 |

|   | A.1           | Safety | Requirements                             | 162 |

|   |               | A.1.1  | Power Up                                 | 162 |

|   |               | A.1.2  | Boot                                     | 162 |

|   |               | A.1.3  | Reset                                    | 162 |

|   |               | A.1.4  | Power Down                               | 162 |

|   |               | A.1.5  | Shutdown                                 | 163 |

|   |               | A.1.6  | Resource Virtualization                  | 163 |

|   |               | A.1.7  | Exclusive Access to Peripherals          | 163 |

|   |               | A.1.8  | Temporal Independence                    | 163 |

|   |               | A.1.9  | Spatial Independence                     | 163 |

|   |               | A.1.10 | Configuration                            | 163 |

|   |               | A.1.11 | Measures and Diagnostic Techniques       | 163 |

|   |               | A.1.12 | System Reactions to Errors               | 164 |

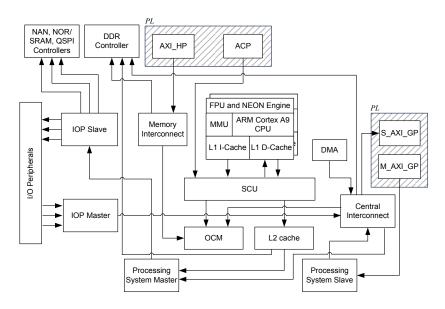

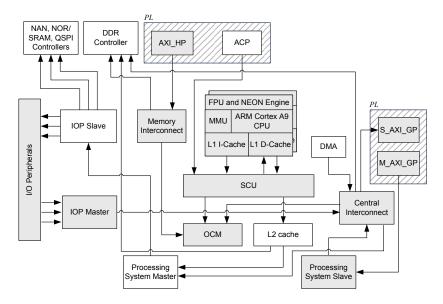

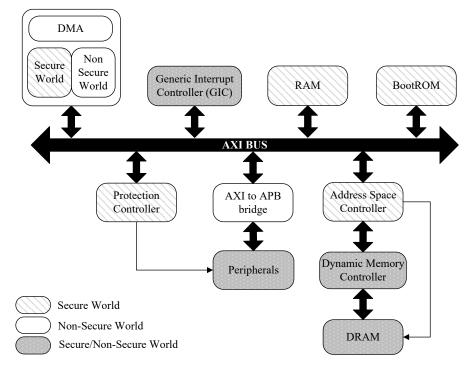

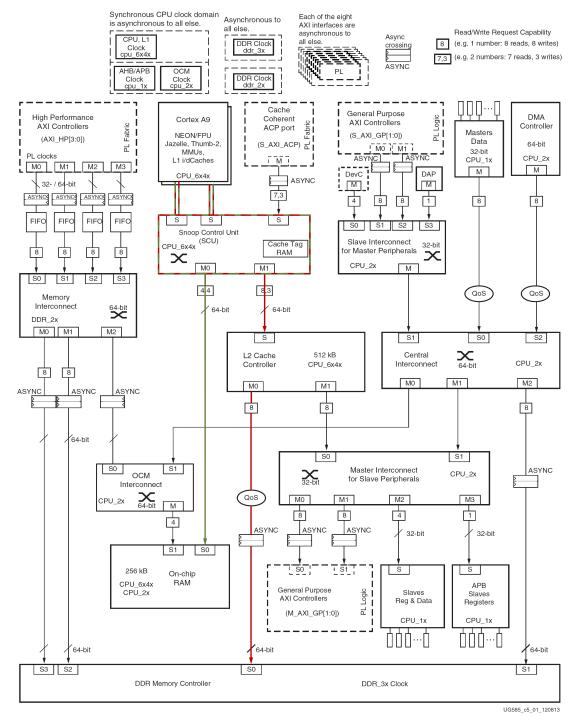

|   | A.2           | Remar  | kable components of the Zynq-7000 device | 180 |

|   |               | A.2.1  | Processing Unit                          | 180 |

|   |               | A.2.2  | Coherency Management Unit                | 180 |

|   |               | A.2.3  | Data Paths                               | 180 |

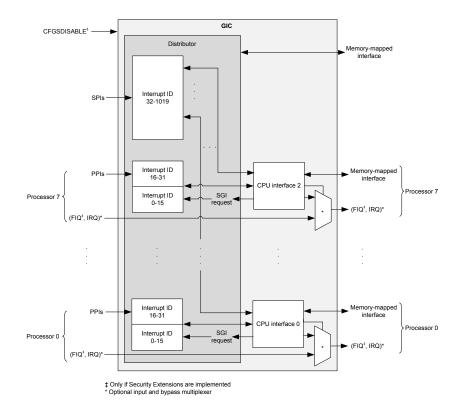

|   |               | A.2.4  | Interrupt Controller                     | 180 |

|   |               | A.2.5  | Memory Areas and Registers               | 180 |

|   |               |        |                                          |     |

#### Publications

# List of Figures

| 1.1          | Structure of the thesis                                                                                                            | 5              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|----------------|

| $2.1 \\ 2.2$ | Safety standards – Hierarchy. (Source IEC 61508-1 [IEC10a])                                                                        | $\frac{8}{10}$ |

| 2.3          | Logical and Physical structure of a mixed-criticality systems – Overview.                                                          | 12             |

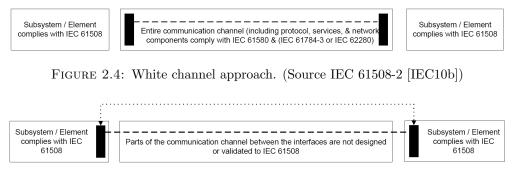

| 2.4          | White channel approach. (Source IEC 61508-2 [IEC10b])                                                                              | 15             |

| 2.5          | Black channel approach. (Source IEC 61508-2 [IEC10b])                                                                              | 15             |

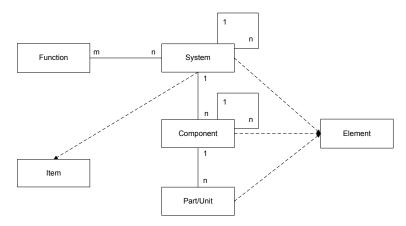

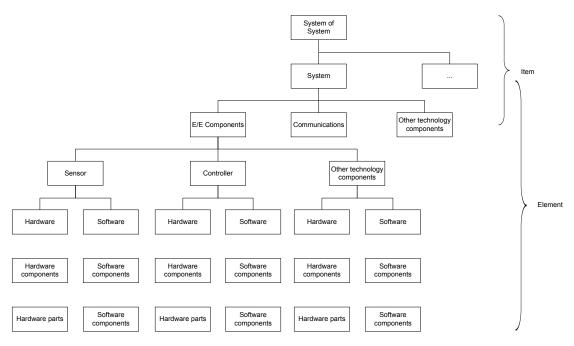

| $3.1 \\ 3.2$ | IEC 61508 – System hierarchy. (Source IEC 61508-1 [IEC10a])<br>ISO 26262 – Relationship of items, system components, Hardware (HW) | 20             |

|              | parts, Software (SW) units and elements. (Source ISO 26262 [ISO09])                                                                | 21             |

| 3.3          | ISO $26262 - \text{Item dissolution.}$ (Source ISO $26262 [\text{ISO09}]$ )                                                        | 21             |

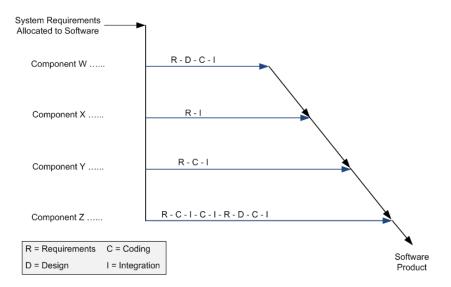

| 3.4          | SW project development sequences. (Source DO-178C [RTC92])                                                                         | 25             |

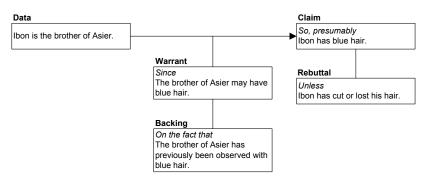

| 3.5          | Toulmin Notation Language – Example.                                                                                               | 26             |

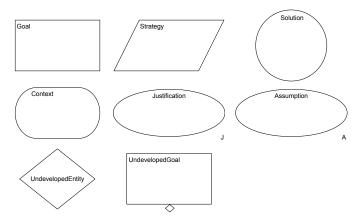

| 3.6          | Goal Structuring Notation (GSN) Elements – Overview                                                                                | 27             |

| 3.7          | GSN – Modularity extensions.                                                                                                       | 27             |

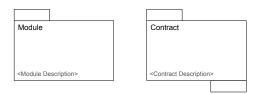

| 3.8          | Claim, Argument and Evidence (CAE) Elements – Overview                                                                             | 28             |

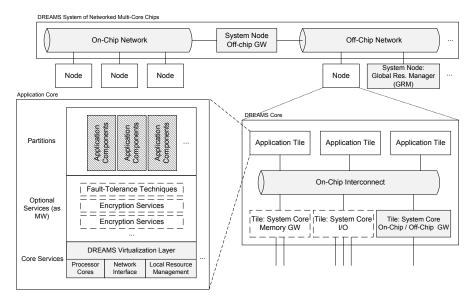

| 4.1          | Distributed REal-time Architecture for Mixed Criticality Systems (DREAMS)<br>Architecture – Overview. (Source [DRE13])             | 32             |

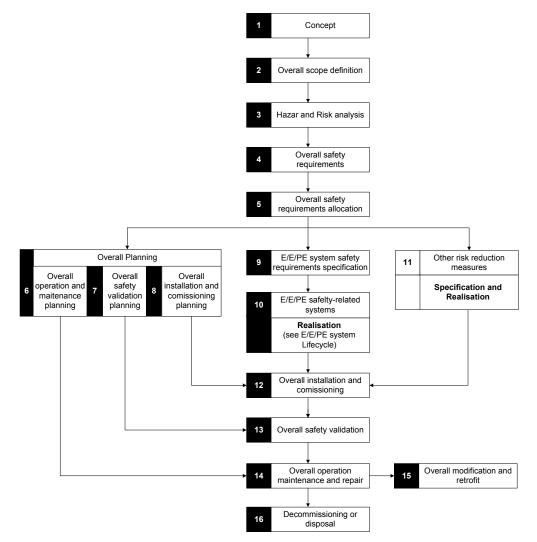

| 4.2          | IEC 61508 – Life cycle. (Source IEC 61508-1 [IEC10a])                                                                              | 33             |

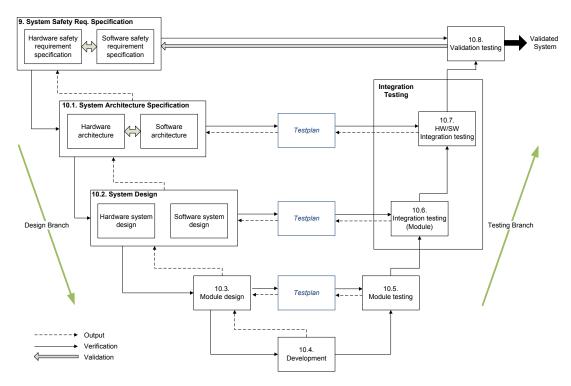

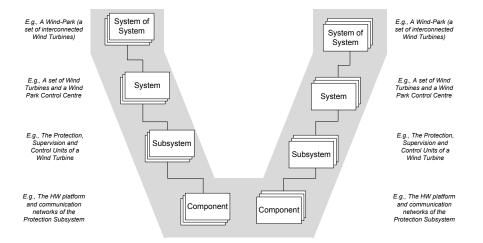

| 4.3          | Safety Life cycle – The V-model.                                                                                                   | 35             |

| 4.4          | Safety approach – Meet-in-the-middle methodology.                                                                                  | 37             |

| 4.5          | Safety approach – Modularity                                                                                                       | 39             |

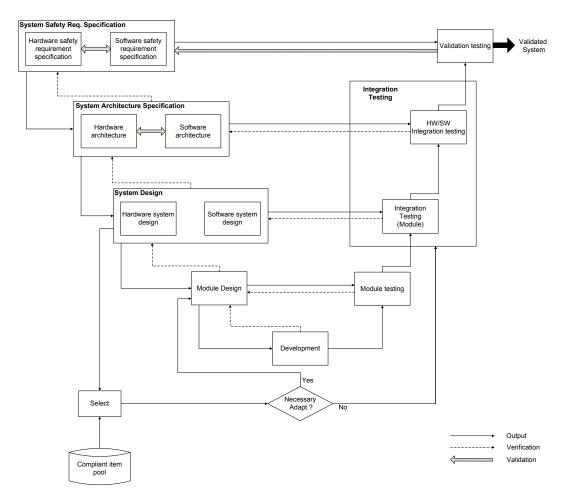

| 4.6          | Component based development process – Safety approach                                                                              | 40             |

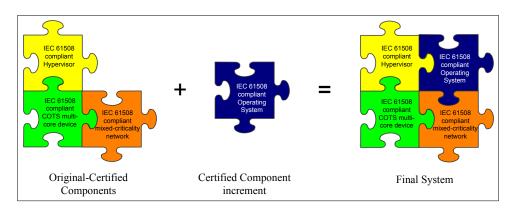

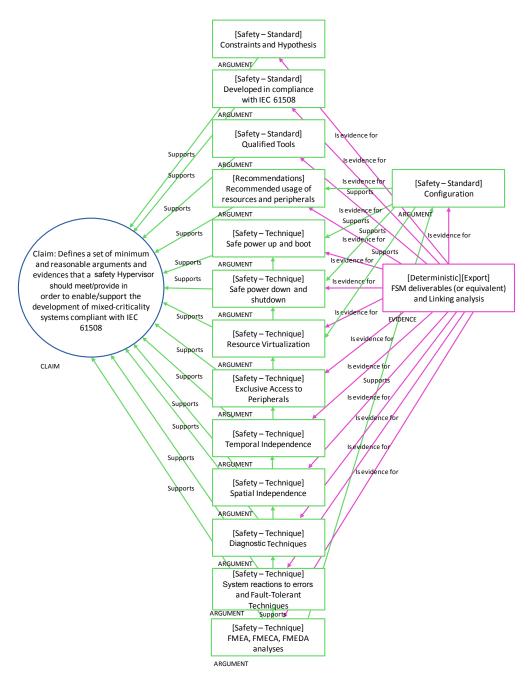

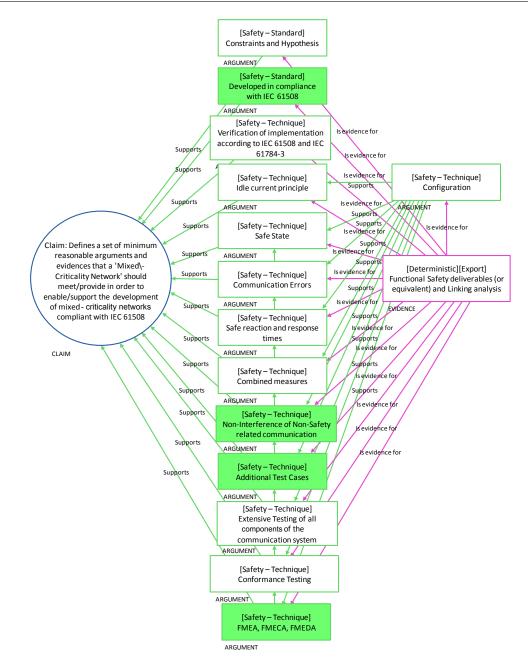

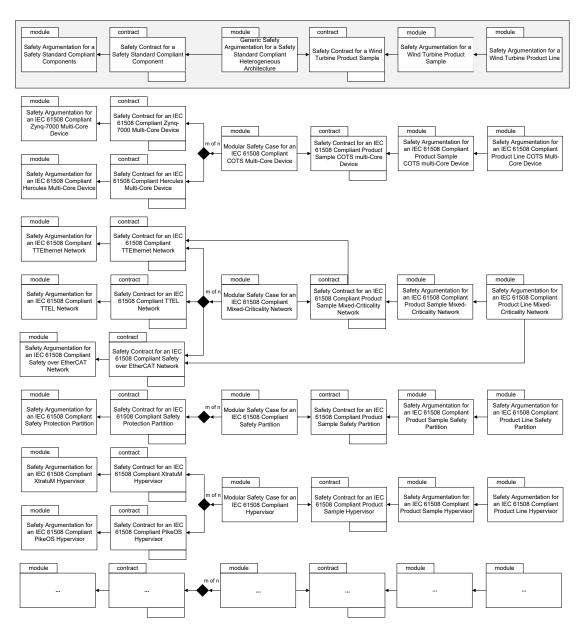

| $5.1 \\ 5.2$ | Modular Certification – Overview                                                                                                   | 41             |

|              | hypervisor – Top                                                                                                                   | 44             |

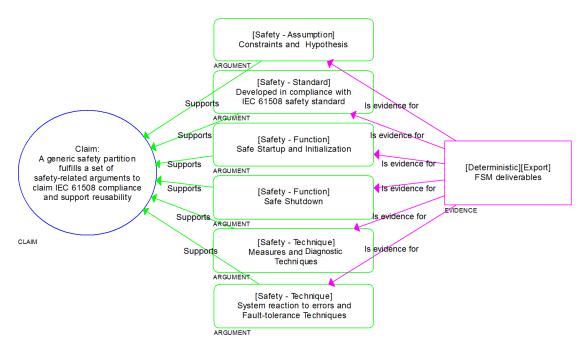

| 5.3          | An MSC for an IEC 61508 compliant generic safety partition – Top                                                                   | 48             |

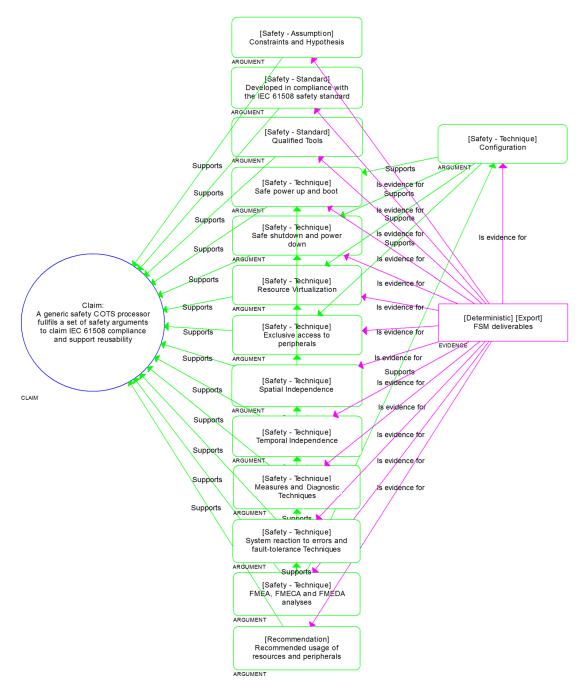

| 5.4          | An MSC for an IEC 61508 compliant generic Commercial off-the-shelf                                                                 |                |

|              | (COTS) multi-core device – Top                                                                                                     | 50             |

| 5.5          | An MSC for an IEC 61508 compliant generic mixed-criticality network – Top                                                          | 55             |

| 6.1          | Dual-port RAM – Overall representation.                                                                                            | 61             |

| 6.2          | $Communication Input/Output (I/O) Server - Overview. \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                                        | 64             |

| 6.3          | Digital Input/Output Server – An overview.                                                                                         | 64             |

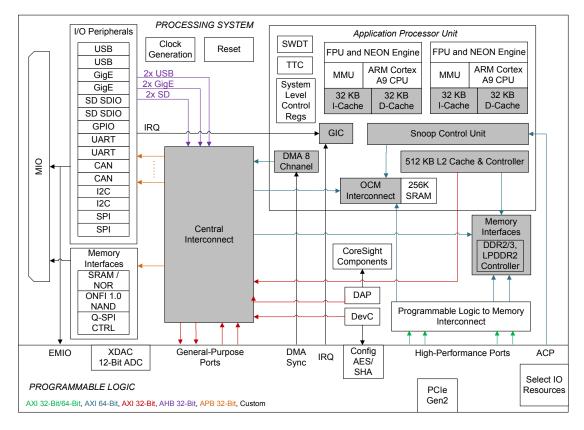

| 6.4          | Zynq-7000 zc706 – Complex and challenging components. (Source [XIL14c])                                                            | 66             |

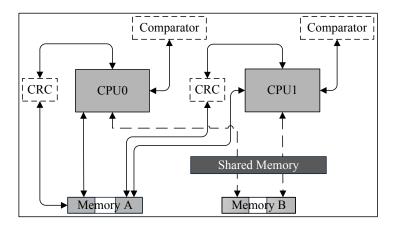

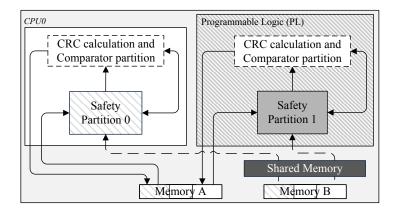

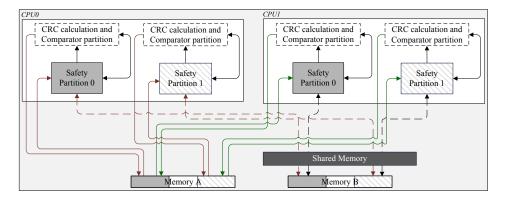

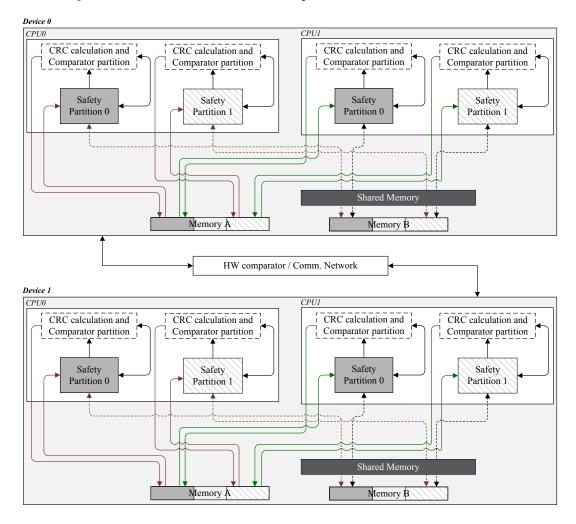

| 6.5   | Shared memory diagnosis pattern – Solution 2: Cyclic Redundancy Check (CRC) with comparison.                                                                   | 68  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.6   | Shared memory diagnosis pattern – Solution 2 – Scenario 1: Non parti-                                                                                          |     |

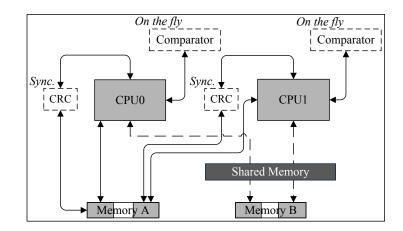

|       | tioned system with the same functionality execution and on-fly comparison.                                                                                     | 70  |

| 6.7   | Shared memory diagnosis pattern – Solution 2 – Scenario 1: Non parti-                                                                                          |     |

|       | tioned system with diverse functionality execution.                                                                                                            | 71  |

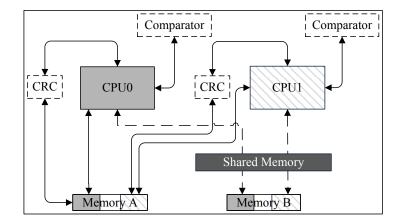

| 6.8   | Shared memory diagnosis pattern – Solution 2 – Scenario 1.3.A.                                                                                                 | 72  |

| 6.9   | Shared memory diagnosis pattern – Solution 2 – Scenario 1.3.B.                                                                                                 | 72  |

| 6.10  | Shared memory diagnosis pattern – Solution 2 – Scenario 2.1: Partitioned                                                                                       | 70  |

| C 11  | system with functionalities with different criticality.                                                                                                        | 73  |

| 0.11  | Shared memory diagnosis pattern – Solution 2 – Scenario 2.2: Partitioned system where safety-related partitions execute the same functionalities.              | 73  |

| 6 1 9 | Shared memory diagnosis pattern – Solution 2 – Scenario 2.3: Partitioned                                                                                       | 15  |

| 0.12  | system with a Processing System (PS) and a Programmable Logic (PL).                                                                                            | 74  |

| 6 13  | Shared memory diagnosis pattern - Solution 2 - Scenario 2.4a: Additional                                                                                       | • • |

| 0.10  | considerations and solutions                                                                                                                                   | 74  |

| 6.14  | Shared memory diagnosis pattern - Solution 2 - Scenario 2.4b: Additional                                                                                       |     |

|       | considerations and solution.                                                                                                                                   | 75  |

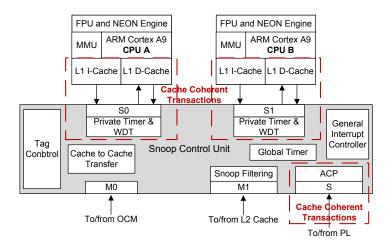

| 6.15  | Coherency management diagnosis pattern – Zynq-7000 multi-core device –                                                                                         |     |

|       | Overview                                                                                                                                                       | 76  |

| 6.16  | Zynq-7000 zc706 – Interconnection scheme – Overview                                                                                                            | 79  |

|       | Interconnection – Certification challenges                                                                                                                     | 79  |

| 6.18  | Generic Interrupt Controller of Zynq-7000 device – Block diagram (Source                                                                                       |     |

|       | [XIL14c])                                                                                                                                                      | 82  |

| 6.19  | Networks-on-Chip (NoC) cross-domain pattern – Overview                                                                                                         | 84  |

| 7.1   | A wind-farm – Overview.                                                                                                                                        | 87  |

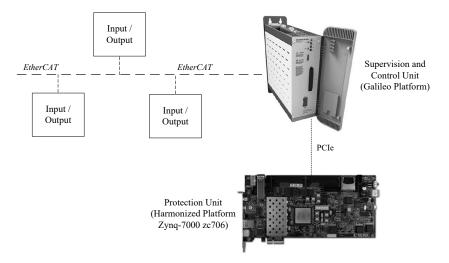

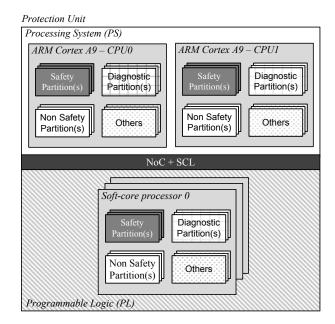

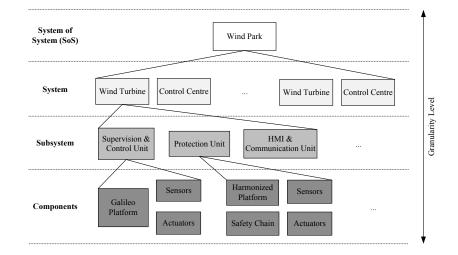

| 7.2   | Wind turbine use case – Overall architecture                                                                                                                   | 89  |

| 7.3   | Wind turbine case study – Block diagram of the protection unit based on                                                                                        |     |

|       | the Zynq-7000 zc706 device.                                                                                                                                    | 90  |

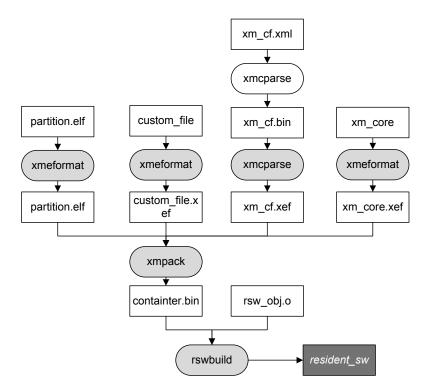

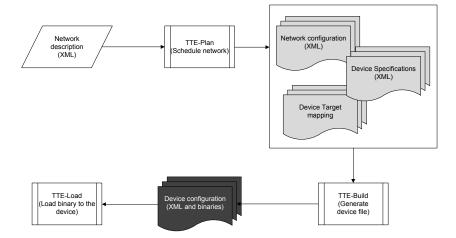

| 7.4   | XtratuM Tool set. (Source DREAMS D5.1.1 Annex A [DRE15])                                                                                                       | 91  |

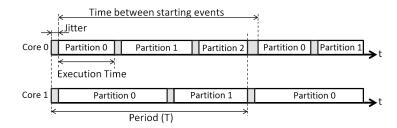

| 7.5   | Cyclic execution scheduling for the XtratuM hypervisor – Example                                                                                               | 93  |

| 7.6   | Partitioned mixed-criticality system – Example                                                                                                                 |     |

| 7.7   | Zynq-7000 – Block diagram. (Source UG585 [XIL14c])                                                                                                             | 97  |

| 7.8   | Zynq-7000 – Normal mode. (Source WP461 [HCM15])                                                                                                                | 97  |

| 7.9   | Zynq-7000 – Lockstep mode. (Source WP461 [HCM15])                                                                                                              |     |

|       | Zynq-7000 – Power Up and Power Down sequences. (Source UG585 [XIL15])                                                                                          |     |

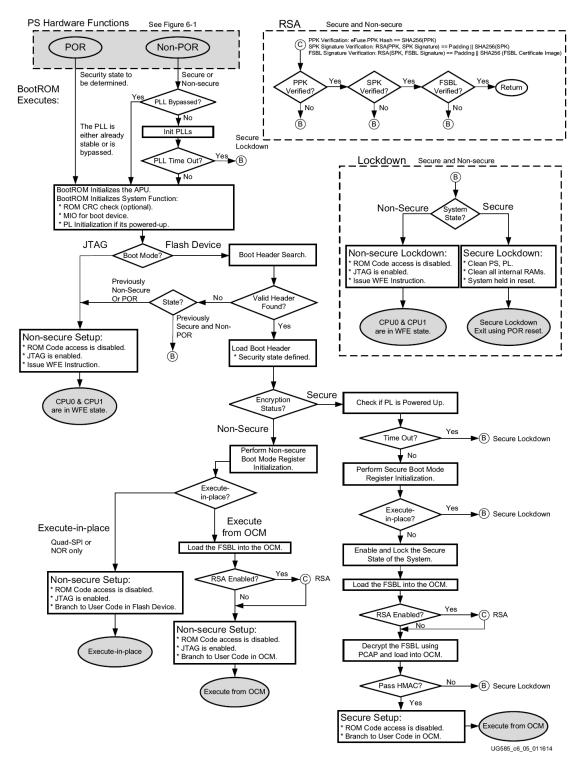

|       | $Zynq-7000 - Boot. (Source UG585 [XIL14c]) \dots \dots$  |     |

|       | Zynq-7000 – Exclusive access to peripherals                                                                                                                    |     |

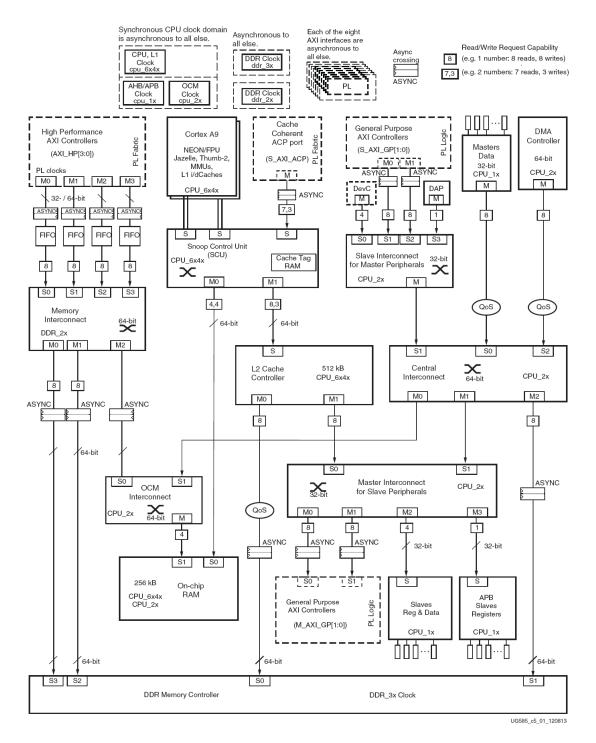

|       | $Zynq-7000 - Interconnect. (Source UG585 [XIL14c]) \dots \dots \dots \dots \dots \square$                                                                      |     |

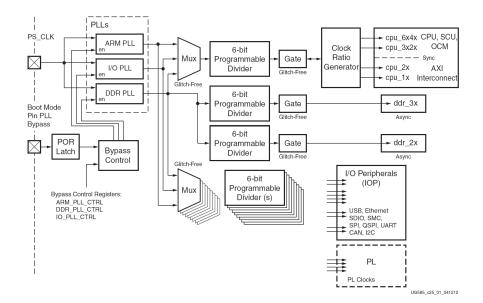

|       | $Zynq-7000 - Clock. (Source UG585 [XIL14c]) \dots \dots$ | 111 |

| (.15  | Time Triggered (TT)Ethernet (TTE) configuration toolset. (Source [TTT15])                                                                                      | 192 |

| 7 16  | Dimensions of abstraction: Development Viewpoint and Granularity Level.                                                                                        |     |

|       | Product line development abstraction layers.                                                                                                                   |     |

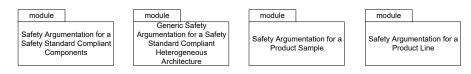

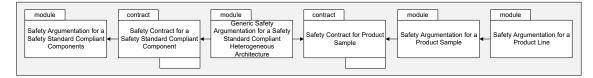

|       | Linkage between the abstraction layers and the contract.                                                                                                       |     |

|       | Automatizing the deployment of a product line                                                                                                                  |     |

|       | Wind Turbine Product Line Safety Argumentation – Example                                                                                                       |     |

| 2     |                                                                                                                                                                | -   |

| 7.21 | Variation points in a Wind Turbine product line – Example                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------|

| 7.22 | Zynq-7000 ZC706 – On-Chip Memory (OCM) and Double Data Rate                                                              |

|      | (DDR) interconnect. (Source [XIL14c]) $\ldots \ldots 132$ |

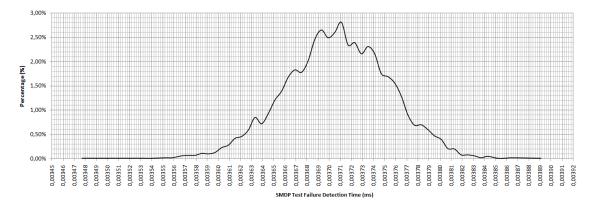

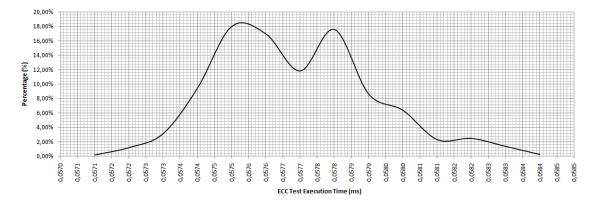

| 7.23 | Shared Memory Diagnostic Pattern (SMDP) – Execution Time Dispersion.133                                                  |

| 7.24 | SMDP – Failure Detection Time Dispersion                                                                                 |

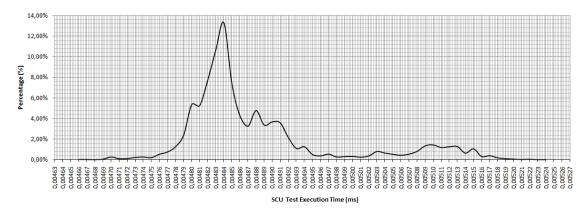

| 7.25 | Coherency Management Unit Diagnostic Pattern (CMUDP) – SCU Con-                                                          |

|      | figuration Test Dispersion                                                                                               |

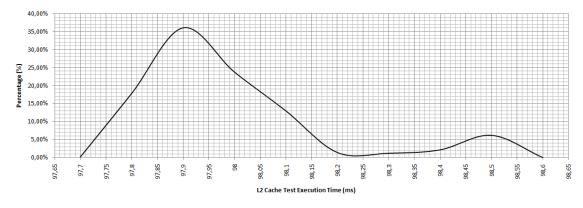

| 7.26 | CMUDP – L2 cache Test Dispersion                                                                                         |

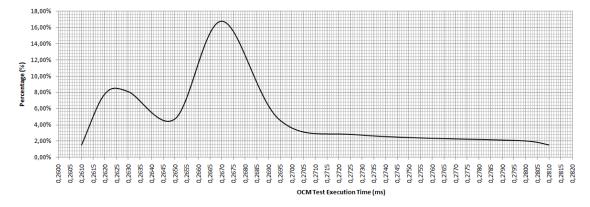

| 7.27 | Coherency Management Diagnostic Pattern – OCM Test Dispersion 140                                                        |

| 7.28 | Coherency Management Diagnostic Pattern – Error Correction Code                                                          |

|      | (ECC) Test Dispersion                                                                                                    |

|      |                                                                                                                          |

# List of Tables

| 2.1          | Custom cross-domain pattern representation template                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2          | Communication errors and combination of measures and detection tech-                                                                            |

| 0.2          | niques – Example. $\ldots$                                     |

|              |                                                                                                                                                 |

| 7.1          | Zynq-7000 – Exclusive Advanced eXtensible Interface (AXI) accesses.                                                                             |

| 7.0          | $(Source [XIL15]) \qquad \dots \qquad $ |

| 7.2          | Zynq-7000 device – TrustZone Security Summary. (Source DS190 [XIL15]) 102                                                                       |

| $7.3 \\ 7.4$ | Reset effects (Source [XIL15])                                                                                                                  |

| 1.4          | failures. <sup>1</sup> (Source Tables A.2 to A.14 of IEC 61508-2 [IEC10b]) 115                                                                  |

| 7.5          | IEC 61508 compliant measures and diagnostic techniques for systematic                                                                           |

| 1.0          | failures. <sup>2</sup> (Source Tables A.15 to A.18 of IEC 61508-2 [IEC10b]) $\ldots \ldots 117$                                                 |

| 7.6          | Safety Communication Layer (SCL) – Communication errors vs Safety                                                                               |

|              | measures. (Source [Eth11])                                                                                                                      |

| 7.7          | SMDP – Implementation results of Scenario 1.1                                                                                                   |

| 7.8          | SMDP – Implementation results of Scenario 1.2                                                                                                   |

| 7.9          | Zynq-7000 zc706 Snoop Control Unit (SCU)'s coherency configuration                                                                              |

|              | registers. (Source [XIL14c]) $\ldots \ldots 134$                   |

| A 1          | Enclose Made and Effects Analysis (EMEA) terrelate                                                                                              |

| A.1<br>A.2   | Failure Mode and Effects Analysis (FMEA) template                                                                                               |

|              | Failure Modes, Effects and Criticality Analysis (FMECA) template 162<br>Power Up – FMEA                                                         |

| A.4<br>A.6   | Boot – FMEA                                                                                                                                     |

|              | Reset – FMEA                                                                                                                                    |

|              | Power Down - FMEA.       100         167                                                                                                        |

|              | 2 Shutdown - FMEA                                                                                                                               |

|              | Resource Virtualization – FMEA                                                                                                                  |

|              | 5 Exclusive access to peripherals – FMEA                                                                                                        |

|              | B   Temporal Independence – FMEA.   1112111111111111111111111111111111111                                                                       |

|              | ) Spatial Independence – FMEA                                                                                                                   |

|              | 2 Configuration – FMEA                                                                                                                          |

|              | Measures and Diagnostic Techniques – FMEA                                                                                                       |

|              | System reactions to errors – FMEA                                                                                                               |

| A.27         | Power Up – FMECA                                                                                                                                |

| A.28         | B Boot – FMECA                                                                                                                                  |

| A.29         | P Reset - FMECA.         172                                                                                                                    |

| A.30         | ) Power Down – FMECA                                                                                                                            |

| A.31         | Shutdown – FMECA                                                                                                                                |

| A.32 Resource Virtualization – FMECA                      |

|-----------------------------------------------------------|

| A.33 Exclusive access to peripherals – FMECA              |

| A.34 Temporal Independence – FMECA                        |

| A.35 Spatial Independence – FMECA                         |

| A.36 Configuration – FMECA                                |

| A.37 Measures / Diagnostic Techniques – FMECA             |

| A.38 System reactions to errors – FMECA                   |

| A.39 SCU – FMEA                                           |

| A.40 Data Paths – FMEA                                    |

| A.41 Generic Interrupt Controller (GIC) Distributor– FMEA |

| A.42 GIC Interrupt Interface– FMEA                        |

| A.43 Memory and Register areas – FMEA                     |

| A.44 Processing Unit – FMECA                              |

| A.45 Memory – FMECA                                       |

| A.46 SCU – FMECA                                          |

| A.47 Data Paths – FMECA                                   |

| A.48 GIC – FMECA                                          |

# Abbreviations

- ACE AXI Coherency Extension

- ACP Accelerator Coherency Port

- **AES** Advanced Encryption Standard

- **AFDX** Avionics Full-Duplex Switched Ethernet

- **AHB** Advanced High-Performance Bus

- AMBA Advanced Microcontroller Bus Architecture

- **APB** Advanced Peripheral Bus

**ARAMIS** Automotive, Railway and Avionics Multicore Systems

- **ASB** Advanced System Bus

- ASCOS Aviation Safety and Certification of new Operations and Systems

- **ASIC** Application Specific Integrated Circuit

- **ASIL** Automotive Safety Integrity Level

- ${\bf AMP}$  Asymmetric MultiProcessing

- ${\bf AXI}$  Advanced eXtensible Interface

- ${\bf BCET}$ Best Case Execution Time

- $\mathbf{BE} \hspace{0.1in} \text{Best-Effort} \hspace{0.1in}$

- **BRAM** Block Random Access Memory (RAM)

- **CAE** Claim, Argument and Evidence

${\bf CC}\,$ Common Criteria

- **CPLD** Complex Programmable Logic Device

- **CONTREX** Design of embedded mixed-criticality CONTRol systems under consideration of EXtra-functional properties

${\bf COTS}$  Commercial off-the-shelf

**CRC** Cyclic Redundancy Check

CMUDP Coherency Management Unit Diagnostic Pattern

**SMDP** Shared Memory Diagnostic Pattern

${\bf CT}\,$  Critical Traffic

**DAS** Distributed Application Subsystem

${\bf DC}\,$  Diagnosis Coverage

**DDRC** DRAM Controller

**DSE** Design Space Exploration

**DIO** Digital I/O

**DIOS** Digital I/O (DIO) Server

**DMA** Direct Memory Access

${\bf DDR}\,$ Double Data Rate

**DECOS** Dependable Embedded Components and Systems

DREAMS Distributed REal-time Architecture for Mixed Criticality Systems

$\mathbf{ECC}\xspace$  Error Correction Code

${\bf ECU}$  Electronic Control Unit

${\bf EDC}\,$  Error Detection Correction

- E/E/PE Electrical / Electronic / Programmable Electronic

- $\mathbf{EMC}^2$  Embedded Multi-Core systems for Mixed Criticality applications in dynamic and changeable real-time environments

- **ET** Event-Triggered

- ${\bf EUC}\,$  Electronic Under Control

- FCU Fault Containment Unit

- ${\bf FTU}$  Fault Tolerant Unit

- **FIQ** Fast Interrupt reQuest

- **FIT** Failure In Time

- FMEA Failure Mode and Effects Analysis

- FMEDA Failure Mode Effects and Diagnostic Analysis

- FMECA Failure Modes, Effects and Criticality Analysis

- FPGA Field Programmable Gate Array

- **FSBL** First Stage Boot Loader

- **FSCP** Functional Safety Communication Profile

- FSM Functional Safety Management

- **FSoE** Functional Safety over EtherCAT

- ${\bf GP}\,$  Generic Product

- **GPSC** Generic Product Safety Case

- **GASC** Generic Application Safety Case

- ${\bf GA}\,$  Generic Application

- **GENESYS** GENeric Embedded SYStem

- **GIC** Generic Interrupt Controller

- ${\bf GRM}\,$ Global Resource Manager

- **GSN** Goal Structuring Notation

- **GUI** Graphical User Interface

- ${\bf HFT}~{\rm HW}$  Fault-Tolerance

| <b>HM</b> Health Monitoring                                         |

|---------------------------------------------------------------------|

| <b>HMAC</b> Hash Message Authentication Code                        |

| <b>HMI</b> Human Machine Interface                                  |

| <b>HP</b> High Performance                                          |

| HSTL High-Speed Transceiver Logic                                   |

| HW Hardware                                                         |

| <b>ICAP</b> Internal Configuration Access Port                      |

| I/O Input/Output                                                    |

| <b>IDF</b> Isolation Design Flow                                    |

| <b>IOP</b> I/O Peripheral                                           |

| <b>IRQ</b> Interrupt Request                                        |

| <b>ISE</b> Integrated Synthesis Environment                         |

| $\mathbf{IVT}$ Isolation Verification Tool                          |

| <b>IT</b> Information Technology                                    |

| LPDDR Low-Power DDR                                                 |

| <b>LRM</b> Local Resource Manager                                   |

| <b>LVCMOS</b> Logic Voltage Complementary Metal-Oxide Semiconductor |

| $\mathbf{M}$ Master                                                 |

| MIO Multiplexed I/O                                                 |

| <b>MMU</b> Memory Management Unit                                   |

| $\mathbf{MPU}$ Memory Protection Unit                               |

| MSC Modular Safety Case                                             |

| MULCORS MULti-core proCessORS in Airbone Systems                    |

${\bf NASA}\,$  National Aeronautics and Space Administration's

#### MultiPARTES Multi-cores Partitioning for Trusted Embedded Systems

- ND Network Description

- NCDB Network Configuration database

- $\mathbf{NC}$  Network Configuration

- $\mathbf{NoC}$  Networks-on-Chip

- **OCM** On-Chip Memory

- **QoS** Quality-of-Service

- **PCI** Peripheral Component Interconnect

- **PCIe** Peripheral Component Interconnect (PCI) Express

- ${\bf PL}$ Programmable Logic

- **PLD** Programmable Logic Device

- **PLL** Phase Locked Loop

- ${\bf POR}\,$  Power On Reset

- $\mathbf{P2P}$  Point-to-Point

- **PPI** Private Peripheral Interrupt

- **PROXIMA** Probabilistic real-time control of mixed-criticality multi-core and manycore systems

- **PS** Processing System

- **PST** Process Safety Time

- **pSafeCer** pilot Safety Certification of Software-Intensive Systems with Reusable Components

- ${\bf RAM}\,$  Random Access Memory

- **RAMS** Reliability, Availability, Maintainability and Safety

- **RC** Rate Constrained

#### ReComp Reduced Certification Costs Using Trusted Multi-core Platforms

- ${\bf RSA}\,$  Rivest, Shamir and Adleman

- **RTCA** Radio Technical Commission for Aeronautics

- ${\bf SA}$  Specific Application

- **SACM** Structured Assurance Case Metamodel

- SASC Specific Application Safety Case

- SASO Safe Autonomous Systems Operations

- SCADA Supervision Control And Data Adquisition

- ${\bf SCL}$ Safety Communication Layer

- SCU Snoop Control Unit

- $\mathbf{SAC} \ \mathrm{SCU} \ \mathrm{Access} \ \mathrm{Control}$

- **SEU** Single Event Upset

- SEM Soft Error Mitigation

- **SGI** SW Generated Interrupt

- **SPI** Shared Peripheral Interrupt

- ${\bf NSAC}\,$  Non Secure SCU Access Control

- **SD** Secure Digital

- **SDL** Security Development Lifecycle

- ${\bf SDK}\,$  SW Development Kit

- ${\bf SEooC}$ Safety Element out of Context

- **SIL** Safety Integrity Level

- **SILCL** Safety Integrity Level Claim Level

- ${\bf SM}\,$  Synchronization Master

- **SMP** Symmetric MultiProcessing

- SoC System on a Chip

- SoS System of System

- SRAC Safety Related Application Conditions

- $\mathbf{STNoC} \ \mathbf{STmicroelectronics'} \ \mathbf{NoC}$

${\bf SW}$  Software

- **TDMA** Time Division Multiple Access

- **TERESA** Trusted Computing Engineering for Resource Constrained Embedded Systems Applications

- ${\bf TLB}\,$  Translation Lookaside Buffer

- ${\bf TMR}\,$  Triple Modular Redundancy

- ${\bf TT}~{\rm Time}~{\rm Triggered}$

- **TTA** TT Architecture

- $\mathbf{TTE} \ \mathbf{TTE} thernet$

- **TTEL** TT Extension Layer

- TTNoC TT Network-on-Chip

- **XADC** Xilinx Analog to Digital Converter

- ${\bf XMCF}\,$  XtratuM Configuration File

- VHDL Very High Speed Integrated Circuit

- $\mathbf{VL}$ Virtual Link

- $\mathbf{VM}$  Virtual Machine

- ${\bf VMM}\,$  Virtual Machine Monitor

- WCET Worst Case Execution Time

- $\mathbf{WDT}\xspace$  Watch Dog Timer

xxvi

Nire guraso, anaia, senide, lagun eta nirekin hiru urte hauetan izan diren denei dedikaturik.

Dedicado a mis padres, hermano, familia, amigos y a todos los que han estado conmigo durante estos tres años.

Dedicated to my parents, brother, family, friends and to those who have supported and encouraged me during these three years.

Gewidmet meiner Familie, meinen Bruder, meinem Freunden und den Personen, die mich über diese drei Jahre unterstützt haben.

xxviii

### Chapter 1

# Introduction

Embedded systems have commonly followed a federated architecture paradigm in which each Distributed Application Subsystem (DAS) is implemented on its stand-alone distributed HW base with a well-defined functionality. However, the soaring demand for high performance and increasing functionality challenges the viability of this approach, leading to the rising trend of moving towards integrated architectures [OKG04] [Ham03]. As a consequence, system engineers aim at the integration of multiple functionalities with different criticality with respect to safety, security and real-time on the same embedded computing platform. A system that combines functionalities of different criticality is often referred to as a mixed-criticality system [Bau11].

The transition from single-core to multi-core architectures has further contributed to this tendency. Multi-core architectures provide benefits in terms of cost, size and weight reduction as well as improved scalability. However, they imply certification challenges (such as the assessment of the temporal independence) which may lead to a significant and potentially unacceptable increase of engineering and certification cost [DAN<sup>+</sup>13, RGG<sup>+</sup>12].

Virtualization mechanisms such as hypervisors are commonly used solutions to tackle challenges related to integrated architectures based on multi-core and many-core processors. These mechanisms limit the impact of changes and faults to reduced areas of the system, enabling in turn reusability and reducing the complexity [Kop08]. A hypervisor is a layer of SW or a combination of SW and HW that enables different independent execution environments on a single computing platform (e.g., XtratuM [Sol14], PikeOS [SYS15]). The execution environments, which are also often referred to as *guest operating systems, virtual machines, partitions* or *domains*, can be designed, developed and certified individually with different criticality levels (e.g., Safety Integrity Level (SIL) 1 to 4 according to the IEC 61508 safety standard). The current integration trend of functionalities with different criticality into a single embedded computing platform may use communication networks with support for different criticality for communication purposes. These communication systems, which are usually referred to as mixed-criticality networks, are capable of supporting safe and predictable message exchanges between DAS with different criticality. Mixed-criticality networks are targeted as the natural replacement of legacy buses in modern system architectures due to their low-cost, high-speed and easy integration with existing network infrastructures. They can be divided into on-chip buses (e.g., Advanced High-Performance Bus (AHB), Advanced System Bus (ASB), Advanced Peripheral Bus (APB)) for communication between the components of the integrated circuits such as the cores of a multi-core processor, off-chip buses (e.g., Ethernet) for inter-node communication (e.g., two devices) and local buses (e.g., PCI, PCI Express (PCIe)) for chip-to-chip interconnect. However, the use of mixed-criticality networks may lead to certification challenges related to the increasing safety, security and real-time constraints in demanding application domains such as automotive and railway.

Certification is a third-party attestation related to products, processes, systems or persons [ISO04]. An attestation is the issue of a statement, based on a decision following reviews, where the fulfilment of specified requirements has been demonstrated. In the safety domain, safety certification is an attestation where an authorised organization or a certification body assesses the fulfilment of the safety requirements of a system regarding specified safety requirements or a safety standard (e.g., IEC 61508, ISO 26262). The traditional approach to certification relies on the certification of the whole system, where the change of a safety aspect of the system implies the re-certification of the entire system. Modularity provides a mechanism for managing the complexity of today's mixed-criticality systems, subdividing the system into smaller parts, also called modules, which can be independently certified and re-used to compose a mixedcriticality system. The certification process of a safety-related system is usually carried out by means of safety cases. A safety case is a documented body of evidences that provides convincing and valid arguments that a system is adequately safe for a given application in a given environment (e.g., automotive, railway, lift). Instead, in modular certification, MSCs are used for evidencing the safety of the components that compose a safety-related system. These safety cases take advantage of the modularity in mixedcriticality system design, allowing assurance of the safety of a system that consists of design modules. This approach is supported by different safety-related standards such as IEC 61508 [IEC10a], ISO 26262 [ISO15a], EN 50129 [EN03] and DO-178 [RTC11] and by many research projects such as the European projects Aviation Safety and Certification of new Operations and Systems (ASCOS) [ASC12], Dependable Embedded Components and Systems (DECOS) [SAS<sup>+</sup>08] and National Aeronautics and Space

Administration's (NASA) Safe Autonomous Systems Operations (SASO) project [DP15] [NAS15].

On the other hand, the measures and diagnostic techniques recommended by today's safety-related standards such as IEC 61508 are geared to single computer systems (see Annex F of IEC 61508-3), where a resource cannot be shared between more than one component at the same time. Instead, multi-core architectures enable sharing a resource between the CPUs at the same time, thus leading to possible interferences in temporal and spatial domains. So, the need for extra measures and diagnostic techniques with support for multi-core devices is identified. However, there are certain exceptions which include non-shared resources of multi-core devices where the measures and diagnostic techniques recommended by those safety standards are applicable (see Tables A.2 to A.14 of IEC 61508-2 [IEC10b]).

#### 1.1 Objective

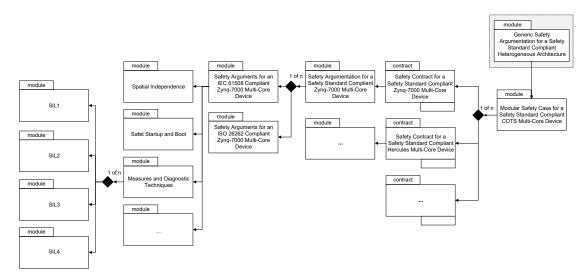

The objectives of this thesis are the definition of generic MSCs for mixed-criticality systems and the definition and implementation of reusable generic cross-domain patterns to solve the certification challenges of today's mixed-criticality systems. These objectives target the key challenges related to certification and mixed-criticality systems which are identified in the introduction.

- Challenges related to certification: Mixed-criticality systems are complex systems that support executing functionalities with different criticality onto the same embedded computing platform. These systems imply several challenges that increase the development and certification cost. In traditional certification, the system is assessed as a whole. Therefore, if a requirement of the system changes, the entire system must be re-certified. This thesis integrates the modularity methodology into the development and certification of mixed-criticality systems to tackle these certification challenges. To that end, this dissertation defines IEC 61508 compliant MSCs for remarkable components of today's mixed-criticality systems such as a hypervisor, a safety partition, a COTS device and a mixed-criticality network.

- Challenges of mixed-criticality systems: Today's safety-related standards (e.g., IEC 61508) focus mainly on single computer architectures where a resource is not shared among more than one component. Instead, multi-core architectures enable sharing a resource between more than one component at the same time. For instance, a memory region can be shared between several processing units of a multi-core device at the same time. This sharing of resources may cause interferences in

the temporal and spatial domains hindering the certification of mixed-criticality systems. Therefore, the measures and diagnostic techniques recommended by those standards are only applicable to single computers. For that reason, the need for new measures and diagnostic techniques with support for multi-core mixedcriticality architectures is identified. This thesis presents reusable generic solutions for mixed-criticality systems which are out of the scope of today's safety-related standards.

#### **1.2** Contributions

The contributions of this dissertation consist of:

- Generic IEC 61508 compliant MSCs for components of today's mixed-criticality systems, including a safety hypervisor (see Section 5.1), a safety partition (see Section 5.2), a safety COTS multi-core device (see Section 5.3) and a mixed-criticality network (see Section 5.4). Modularity enables the division of the system into modules which can be independently assessed and re-used for developing a mixed-criticality system.

- Reusable and generic cross-domain patterns for partitioned and networked multicore mixed-criticality systems. These patterns provide reusable solutions, measures and diagnostic techniques to solve, detect and avoid the key issues of today's mixedcriticality systems which are not considered by current safety-related standards (see Chapter 6).

The MSCs and cross-domain patterns defined throughout this dissertation can be integrated into different domain case studies (e.g., railway, automotive, wind-power, healthcare, lift). The solutions presented in this thesis are integrated into a wind turbine case study that complies with the architecture style of the European research project DREAMS (see Chapter 4) and the IEC 61508 safety standard.

#### 1.3 Structure of this Thesis

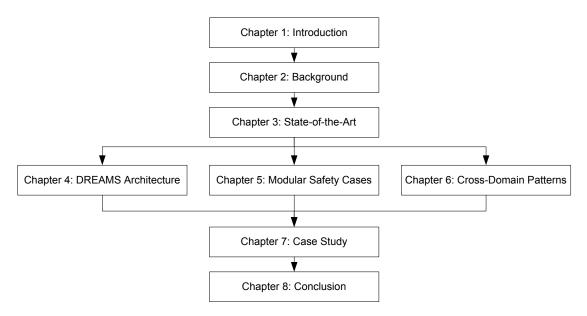

This thesis is organised as described below and as shown in Figure 1.1.

• Chapter 2 introduces the basic concepts on which the work of this thesis is based.

- Chapter 3 analyses the state-of-the-art of the modularity among different safety standards (e.g., IEC 61508 and ISO 26262) and defines the remarkable safety case notation languages.

- Chapter 4 defines the architecture style of the European research project DREAMS.

- Chapter 5 presents the MSCs for an IEC 61508 compliant generic hypervisor, partition, COTS multi-core processor and mixed-criticality network.

- Chapter 6 analyses the recurring problems in the development and certification process of today's mixed-criticality systems by cross-domain patterns. In addition, this chapter defines several remarkable cross-domain patterns that aim to solve the commonly occurring problems in mixed-criticality systems.

- Chapter 7 presents the wind turbine case study where the main contributions of this thesis are integrated.

- Chapter 8 shows the conclusions and future work.

FIGURE 1.1: Structure of the thesis.

## Chapter 2

# Background

This chapter introduces the basic concepts on which the work presented in this thesis is based.

## 2.1 Mixed Criticality Systems

A mixed-criticality system refers to the integration of HW, operating system, middleware services and software applications (e.g., safety-critical, non safety-critical) on the same embedded computing platform [Com12, WESK10]. This approach enables the reduction of devices, wires, and connectors, thereby improving the overall cost-size-weight factor and scalability. However, mixed-criticality systems, especially multi-core mixed-criticality systems, give rise to challenges related to certification (e.g., the assurance of temporal independence) [ESEH<sup>+</sup>12, PGT<sup>+</sup>13, PGN<sup>+</sup>14].

There are many running or just finished research projects in the field of multi-core and mixed-criticality technology funded by the European Union (e.g., DREAMS [DRE13], Design of embedded mixed-criticality CONTRol systems under consideration of EXtrafunctional properties (CONTREX) [CON14], Probabilistic real-time control of mixedcriticality multi-core and manycore systems (PROXIMA) [PRO14]), national bodies (e.g., Automotive, Railway and Avionics Multicore Systems (ARAMIS) project [ARA11]) and a mix of European and national funding (e.g., ARTEMIS Embedded Multi-Core systems for Mixed Criticality applications in dynamic and changeable real-time environments (EMC<sup>2</sup>) [EMC14]).

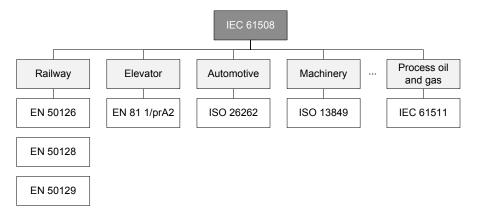

## 2.2 Certification Standards

Certification is a third-party attestation related to products, processes, systems or persons [ISO04]. An attestation is the issue of a statement, based on a decision following reviews, where the fulfilment of specified requirements has been demonstrated. Safety certification attests that a system is safe enough for its purpose with a given confidence level and in a given environment. For instance, IEC 61508 [IEC10a, IEC10b, IEC10c] is the generic international standard for Electrical / Electronic / Programmable Electronic (E/E/PE) functional safety systems and it is the reference safety standard for different domain-specific safety standards such as machinery, industrial process, automotive and railway (see Figure 2.1). IEC 61508 defines the concept of SIL as a relative level of risk-reduction provided by a safety-related system with values in the range from 1 to 4. SIL1 is the lowest value and SIL4 is the most restrictive one. As a general rule, the highest SIL has the highest certification cost.

FIGURE 2.1: Safety standards – Hierarchy. (Source IEC 61508-1 [IEC10a])

### 2.2.1 Fail-Safe and Fail-Operational Systems

Safety-critical systems can be classified as *fail-safe* or *fail-operational* [Kop11]. A system is *fail-safe* when in the event of a failure a safe state can be reached. For example, a train can be stopped in the case of a failure, leading it to a safe state. Conversely, a system that must remain operational even after the occurrence of a fault, i.e., cannot reach a safe state, is called a *fail-operational* system. For example, an aircraft cannot reach a safe state while in flight, it must continue flying although a failure occurs.

### 2.3 Dependability

Dependability refers to the ability to provide services that can defensibly be trusted at a time. These services can be provided to system users such as human users or computer systems [ALRL04]. Whenever the behaviour of a system deviates from the expected intended usage, it is considered that the system fails. An *error* is part of the system state that may cause a subsequent *failure*. A *fault* is the adjudged or hypothesised cause of an error. Dependability can also be defined as the measure of a system's *reliability*, *safety*, *maintainability*, *availability* and *security* attributes.

- *Reliability (MTTF)* refers to the probability that a system will provide specific services until a given time, considering that the system is operational at the beginning.

- Safety is reliability regarding critical failure modes. The failure modes can be malign or benign. Malign failure modes are concerned to critical failure modes while benign failure modes are considered non-critical failures. For example, the crash of an aeroplane due to a failure in the flight-control system is regarded as a malign failure mode.

- *Maintainability (MTTR)* is a measure of the time interval required to repair a system after the occurrence of a benign failure.

- Availability (A) is a measure of the delivery of the correct service given the alternation of correct and incorrect services. Availability is related to the reliability and maintainability attributes as follows:

$$A = MTTF / (MTTF + MTTR)$$

• *Security* is concerned with the authenticity and integrity of information and the ability of a system to prevent unauthorised accesses to information or services.

## 2.4 Fault Containment

Fault containment refers to design and engineering efforts that ensure that the immediate consequences of a fault are limited to a single Fault Containment Unit (FCU) [Kop11]. An FCU is the specification of the units of failure that can impact on the overall reliability of a system. The quality engineer must ensure that FCUs fail independently. Otherwise,

if they fail at the same time, they will have a substantial impact on the overall reliability of the system.

In a distributed system, a HW or a SW component can be considered to form an FCU. For instance, on a multi-core processor, a core that communicates with other cores through messages can be deemed to constitute an FCU. However, since the cores of a multi-core processor are physically close together, share a common power supply and a common timing source, the independence of the failures of the cores cannot be justified. For example, in the E/E/PE safety function or the automotive domain, the compliance to SIL3 or Automotive Safety Integrity Level (ASIL) D means that a maximum of one dangerous error within  $10^{-7}$  operating hours is acceptable [ISO15b].

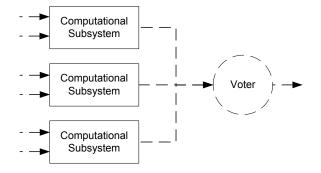

Fault Tolerant Units (FTUs) tolerate the failures of FCUs. An FTU masks the failure of an FCU inside. To that purpose, an FCU can implement the fail-silent abstraction. A fail-silent FCU consists of a computational subsystem and an error monitor or two FCUs and a result comparator. In addition, if no assumptions about the failure behaviour of the FCU can be made, i.e., Byzantine failures,<sup>1</sup> then the Triple Modular Redundancy (TMR) may be needed. In TMR, an FTU consists of three synchronised replica deterministic FCUs composed of a voter and the computational subsystems which may communicate through a real-time communication network such as shown in Figure 2.2.

FIGURE 2.2: Triple Modular Redundancy – Overview.

## 2.5 Complexity Management

As stated in Section 2.1, the integration of applications with different criticality on a single embedded computing platform improves scalability and reduces the number of the system's wires and connectors, thereby improving the cost-size-weight factor. For instance, a system can be composed of tens/hundreds of SW partitions that communicate through an on-chip and/or off-chip mixed-criticality network and execute on the cores in case of the on-chip networks and devices in case of off-chip networks [Kop08].

<sup>&</sup>lt;sup>1</sup>An error that occurs when a set of receivers observes different values of a real-time entity.

The system architect plays a key role in the specification and design of mixed-criticality systems and the selection of appropriate safety techniques for the system level. In addition, the system architect must provide sufficient evidence to the claim that the overall system is safe to the Reliability, Availability, Maintainability and Safety (RAMS) team and the external certification authorities. The availability of complexity management strategies should ease the development, maintenance and certification of mixed-criticality systems. As stated in [Kop08], four basic simplification strategies can be applied to manage the complexity and overcome human limited cognitive capabilities.

- Abstraction refers to the formation of a higher-level concept that captures the essence of the problem-at-hand and reduces the complexity of the scenario by omitting irrelevant details. In a scenario with tens/hundreds of building blocks, which can be custom implementations, COTS or developed by a third party, abstraction becomes a key concern for the system architect.

- *Partitioning* refers to the spatial division of a problem using a *divide and conquer* approach. This is applied, for example using SW partitions.

- *Isolation* refers to the suppression of irrelevant details from the specification of cause and an effect.

- Segmentation refers to the temporal decomposition of complex behaviour into smaller parts that can be processed sequentially. This is applied, for example, using SW partition schedules (e.g., periodic cyclic scheduling with pre-assigned time slots).

### 2.6 Structuring of Mixed-Criticality Embedded Systems

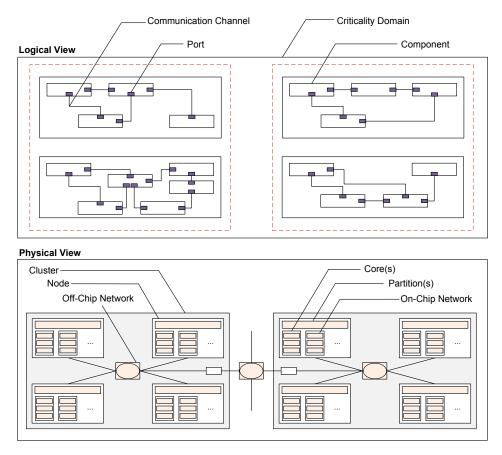

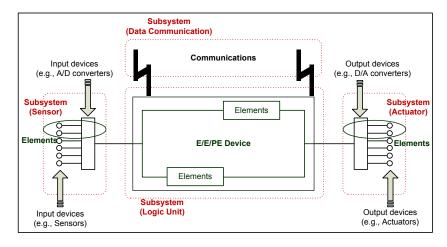

Mixed-criticality embedded systems consist of *physical* and *logical* structures (See Figure 2.3). Physically, a mixed-criticality system consists of a set of *clusters* that contain *nodes*. Each node is a multi-core chip containing *tiles* that is interconnected through a real-time communication network. The tiles provide network interfaces (NI) to the network and offer ports for the transmissions or receptions of the NoC's messages [DRE13].

A tile can be a processor cluster with several processor cores, caches, local memories and I/O resources. Alternatively, a tile can also be a single processor core or an IP core (e.g., memory controller that is accessible using the NoC and shared by several other tiles). Off-chip and on-chip networks are responsible for time and space partitioning between nodes or tiles respectively. They ensure that a node or tile cannot affect the guaranteed timing (e.g., bounded latency and jitter, guaranteed bandwidth) and the

FIGURE 2.3: Logical and Physical structure of a mixed-criticality systems – Overview.

integrity of messages sent by other nodes and tiles. The processor cores within a tile can run a hypervisor (see Section 2.8) that establishes partitions, each of which executes a corresponding SW component. The hypervisor establishes time and space partitioning, thereby ensuring that a SW component cannot affect the availability of the computational resource in other partitions (e.g., time and duration of execution on the processor core, integrity and timing of memory).

On the other hand, the overall logical structure of a mixed-criticality system is structured into criticality levels. Several criticality levels can be distinguished in different application domains such as SIL1 to 4 in IEC 61508, classes A to E in avionics and ASILA to D in automotive. For each criticality level, there can be multiple application subsystems with different safety assurance levels. These subsystems can be further subdivided into components (e.g., processing memory and I/Os). Each component provides services to its environment and interacts by the exchange of messages via ports. TT, Rate Constrained (RC) and Best-Effort (BE) types of messages can be distinguished based on the timing of the messages.

## 2.7 Partitioning in Time and Value Domains

Partitioning is a requisite for modular certification that ensures the independence regardless of design faults affecting the components of a system. In modular certification, each application subsystem is certified to the respective level of criticality (e.g., SIL1 to 4 according to the IEC 61508 safety standard). The partitions for mixed-criticality systems are usually realised by operating systems and hypervisors (see Section 2.8 with time and space partitioning). In the temporal domain, scheduling mechanisms that assign available resources to tasks based on fixed periodic time slots are applied. On the other hand, spatial partitioning can be achieved by allocating a partition to an address space which is not accessible by other partitions. A partitioned system offers many appealing benefits such as memory protection (space partitioning), execution guarantees (time partitioning) and improved fault containment capabilities.

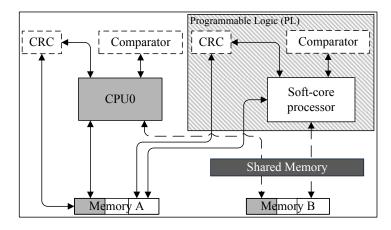

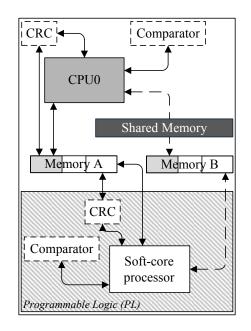

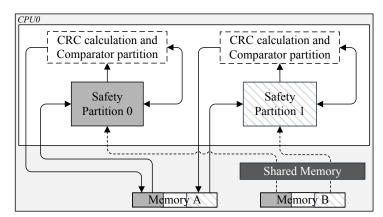

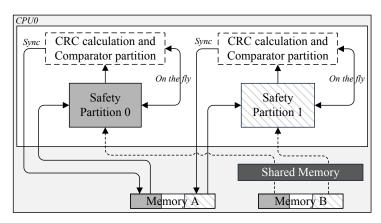

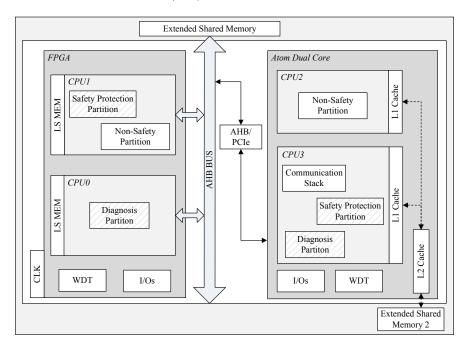

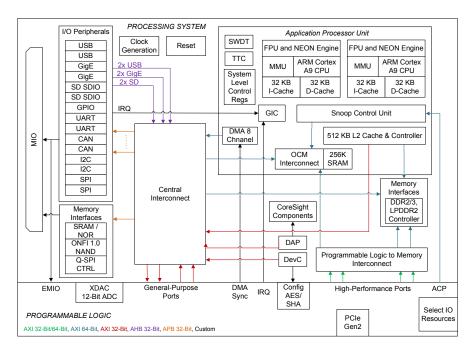

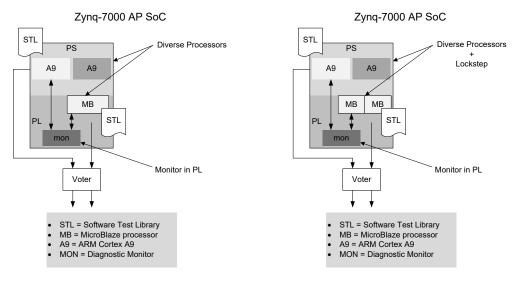

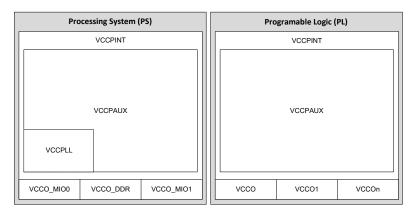

## 2.8 Virtualization