# Execution Environment for Integrated Real-Time Systems based on Software-Defined Networking

DISSERTATION

zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften (Dr.-Ing.)

> vorgelegt von M.Sc. Hongjie FANG geb. am 26.11.1990 in Guangdong, China

eingereicht bei der Naturwissenschaftlich-Technischen Fakultät der Universität Siegen Siegen 2019

Gedruckt auf alterungsbeständigem holz- und säurefreiem Papier.

Betreuer und erster Gutachter Prof. Dr. Roman Obermaisser Universität Siegen

Zweiter Gutachter Prof. Dr. Raimund Kirner University of Hertfordshire

Tag der mündlichen Prüfung 13.05.2020

This dissertation is dedicated to my beloved wife and my parents.

v

# Acknowledgements

I would like to express my sincere appreciation and heartfelt thanks to my advisor Mr. Prof. Dr. Roman Obermaisser for his invaluable guidance during the process of my PhD research. Mr. Prof. Dr. Roman Obermaisser provided me constructive suggestions and generous assistance throughout our cooperation in the last years. Moreover, I appreciate the professional support and advice provided by the members of my examination committee, which essentially helped me to improve my dissertation.

I would also like to acknowledge the unconditional love and support from my wife, which inspires and motivates me to overcome the difficulties during this phase of my life. My sincere thanks to my parents for their infinite support in my academic career, and their beliefs in me to reach my goals in my life.

Finally, many thanks to all my friends and colleagues for your encouragement. It is a precious memory in my life to know you and work with you.

# Abstract

Today there exists a wide range of industrial systems that are based on federated architectures, which means that the each computing node in the system is exclusively assigned to one function. Due to the increasing computing capability of a single processor and the increasing amount of computing processors on a single platform, extensive research on integrating multiple functions with different criticality levels on a shared platform was carried out. For example, in the avionic domain, the development trend has moved from federated to integrated architectures. The ARINC 653 standard was released, which defines the execution environment for hosting several avionic software functions within a single computing node. ARINC 653 was successfully implemented (e.g., Airbus A380) and achieved its primary goals (cost and weight reduction, enabling modular certification).

However, the existing execution environments based on an integrated architecture support only static system configurations. In specific domains like the railway industry, dynamic system adaptation is required during runtime, which affects both the application execution environment and the data communication mechanisms. In this dissertation, our focus is on an execution environment based on an integrated architecture, which guarantees the safe integration of mixed-criticality applications and also addresses the system reconfiguration problem.

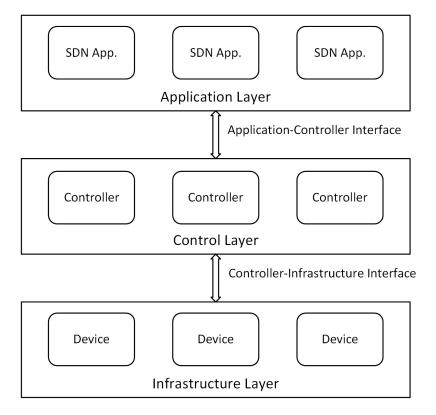

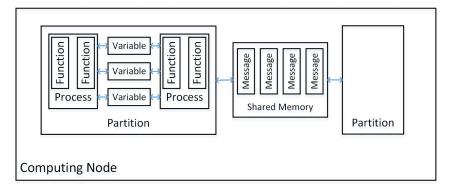

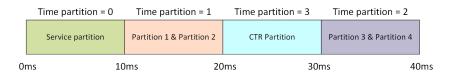

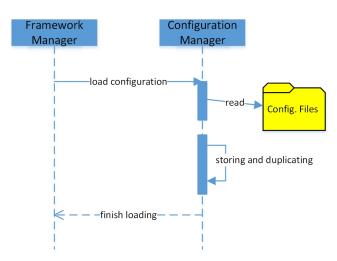

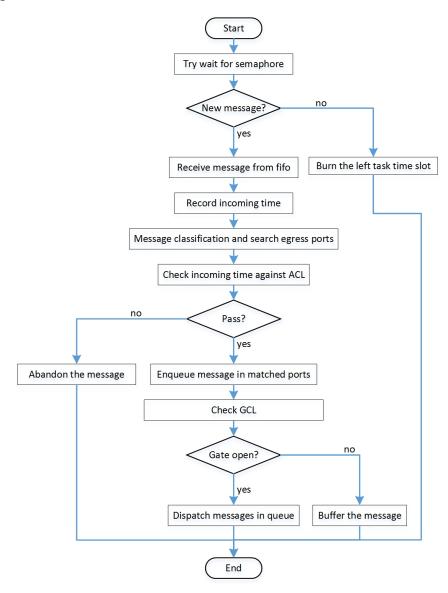

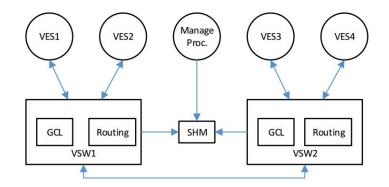

In order to close the research gap, we introduce an execution environment for integrated real-time applications by leveraging the Software-Defined Networking (SDN) paradigm. We extend the temporal and spatial isolation mechanisms from the application layer to the execution environment, so that the integrated applications share the computing node without interference. For the data communication of the integrated applications, we propose a virtual switch supporting temporal and spatial isolation between data flows and leverage the SDN paradigm to address the reconfiguration requirements of data flows. Besides, we also address the controlled import and export of messages between data flows in the proposed virtual switch. For the deterministic communication requirements of hard real-time applications, we propose a virtual switch that is IEEE 802.1Qbv and IEEE 802.1Qci capable according to the Time Sensitive Networking (TSN) standard, in order to close the research gap of virtual switching guaranteeing bounded delay with low jitter in an integrated architecture.

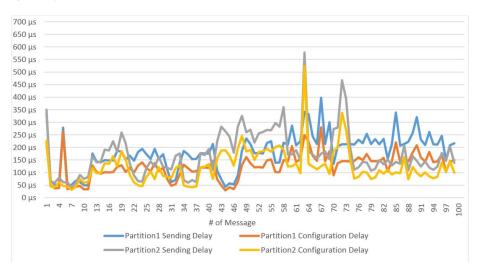

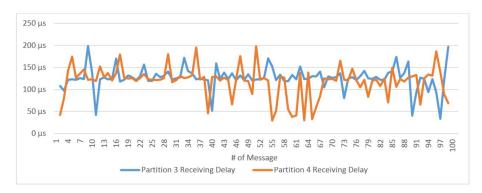

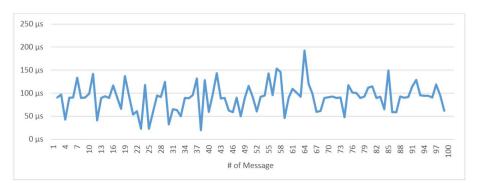

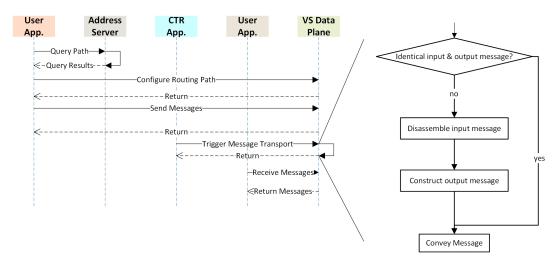

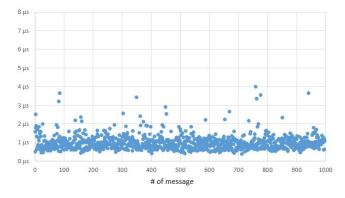

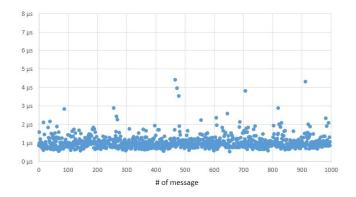

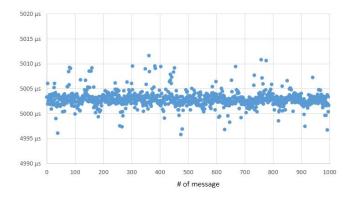

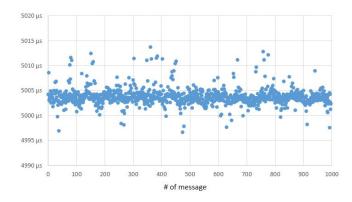

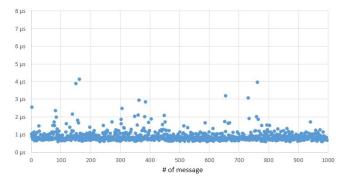

In the proof-of-concept implementations, we demonstrate the non-interference between applications in the execution environment by fault injection. In our virtual switch demonstrators, we evaluate the fundamental isolation mechanisms and determinism of message switching, while measuring the caused overhead for message transmission as well as controlled data exchange, where the measured overhead in the proposed virtual switch is less than 10  $\mu$ s.

x

# Kurzfassung

Heute gibt es eine breite Palette von Industriesystemen, die auf föderierten Architekturen basieren, was bedeutet, dass jeder Rechenknoten im System ausschließlich einer Funktion zugeordnet ist. Aufgrund der zunehmenden Rechenleistung eines einzelnen Prozessors und der zunehmenden Anzahl von Rechenprozessoren auf einer einzigen Plattform wurde umfangreiche Forschung zur Integration mehrerer Funktionen mit unterschiedlichen Kritikalitätsstufen auf einer gemeinsamen Plattform durchgeführt. So hat sich beispielsweise im Bereich der Avionik der Entwicklungstrend von föderierten zu integrierten Architekturen verlagert. Der ARINC 653 Standard wurde veröffentlicht, der die Ausführungsumgebung für das Hosting mehrerer Avionik-Softwarefunktionen in einem einzigen Rechenknoten definiert. ARINC 653 wurde erfolgreich implementiert (z.B. Airbus A380) und erreichte seine primären Ziele (Kosten- und Gewichtsreduzierung, modulare Zertifizierung möglich).

Die bestehenden Ausführungsumgebungen auf Basis einer integrierten Architektur unterstützen jedoch nur statische Systemkonfigurationen. In bestimmten Bereichen wie der Bahnindustrie ist eine dynamische Systemanpassung zur Laufzeit erforderlich, die sowohl die Anwendungsausführungsumgebung als auch die Datenkommunikationsmechanismen betrifft. In dieser Dissertation liegt unser Fokus auf einer Ausführungsumgebung, die auf einer integrierten Architektur basiert, die die sichere Integration von mixed-criticality-Anwendungen garantiert und auch das Problem der Systemrekonfiguration angeht.

Um die Forschungslücke zu schließen, stellen wir eine Ausführungsumgebung für integrierte Echtzeitanwendungen vor, indem wir das Paradigma des Software-Defined Networking (SDN) nutzen. Wir erweitern die zeitlichen und räumlichen Isolations-mechanismen von der Anwendungsschicht auf die Ausführungsumgebung, so dass sich die integrierten Anwendungen den Rechenknoten störungsfrei teilen. Für die Datenkommunikation der integrierten Anwendungen schlagen wir einen virtuellen Switch vor, der die zeitliche und räumliche Isolation zwischen den Datenflüssen unterstützt und das SDN-Paradigma nutzt, um die Rekonfigurationsanforderungen der Datenflüsse zu erfüllen. Darüber hinaus befassen wir uns auch mit dem kontrollierten Import und Export von Nachrichten zwischen Datenflüssen im vorgeschlagenen virtuellen Switch. Für die deterministischen Kommunikationsanforderungen von harten Echtzeitanwendungen schlagen wir einen virtuellen Switch vor, der IEEE 802.1Qbv und IEEE 802.1Qci nach dem Time Sensitive Networking (TSN)-Standard ist, um die Forschungslücke des virtuellen Switchings zu schließen, das eine begrenzte Verzögerung mit geringem Jitter in einer integrierten Architektur garantiert.

In den Proof-of-Concept-Implementierungen zeigen wir die Nicht-Interferenz zwischen Anwendungen in der Ausführungsumgebung durch Fehlerinjektion. In unseren Virtual-Switch-Demonstratoren bewerten wir die grundlegenden Isolationsmechanismen und den Determinismus des Message-Switching, während wir den verursachten Overhead für die Nachrichtenübertragung sowie den kontrollierten Datenaustausch messen, wobei der gemessene Overhead im vorgeschlagenen Virtual-Switch weniger als 10  $\mu$ s beträgt.

# Contents

| A  | cknov  | wledge  | ments      |                          | vii  |

|----|--------|---------|------------|--------------------------|------|

| Al | bstrac | ct      |            |                          | ix   |

| Kı | urzfa  | ssung   |            |                          | xi   |

| 1  | Intr   | oductio | on         |                          | 1    |

|    | 1.1    | Proble  | em Staten  | nent                     | . 2  |

|    | 1.2    | Contr   | ibutions   |                          | . 3  |

|    | 1.3    | Docu    | ment Stru  | cture                    | . 4  |

| 2  | Basi   | ic Conc | epts and   | Terms                    | 5    |

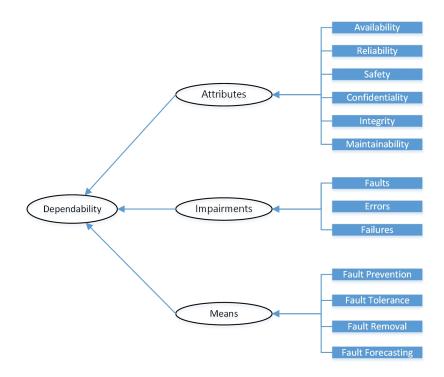

|    | 2.1    | Deper   | ndability  |                          | . 5  |

|    |        | 2.1.1   | Attribut   | æs                       | . 5  |

|    |        |         | 2.1.1.1    | Availability             | . 5  |

|    |        |         | 2.1.1.2    | Reliability              | . 6  |

|    |        |         | 2.1.1.3    | Safety                   | . 6  |

|    |        |         | 2.1.1.4    | Confidentiality          | . 7  |

|    |        |         | 2.1.1.5    | Integrity                | . 7  |

|    |        |         | 2.1.1.6    | Maintainability          | . 7  |

|    |        | 2.1.2   | Impairn    | nents                    | . 7  |

|    |        | 2.1.3   | Fault Cl   | asses                    | . 8  |

|    |        |         | 2.1.3.1    | Hardware Faults          | . 8  |

|    |        |         | 2.1.3.2    | Software Faults          | . 8  |

|    |        |         | 2.1.3.3    | Interaction Faults       | . 8  |

|    |        | 2.1.4   | Means o    | of Dependability         | . 8  |

|    |        |         | 2.1.4.1    | Fault Prevention         | . 8  |

|    |        |         | 2.1.4.2    | Fault Tolerance          | . 9  |

|    |        |         | 2.1.4.3    | Fault Removal            | . 9  |

|    |        |         | 2.1.4.4    | Fault Forecasting        | . 9  |

|    | 2.2    | System  |            | cture                    |      |

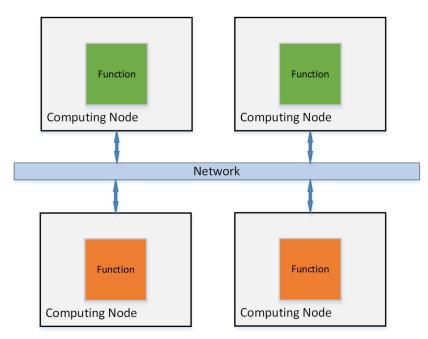

|    |        | 2.2.1   | Federat    | ed Architecture          | . 10 |

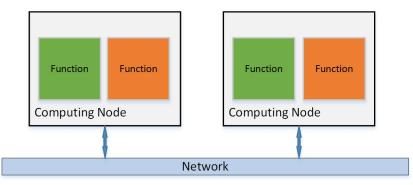

|    |        | 2.2.2   | 0          | ed Architecture          |      |

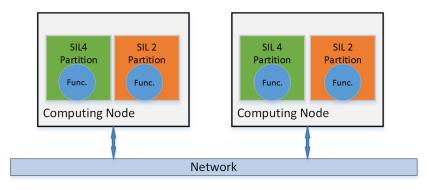

|    |        | 2.2.3   | Mixed-0    | Criticality Architecture | . 11 |

|    |        | 2.2.4   | Executio   | on Environment           | . 12 |

|    | 2.3    | Real-7  | Time Syste | ems                      | . 12 |

xiv

|   |                                   | 2.3.1                                                                                | Hard Real-Time System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                                                                                                                                 |

|---|-----------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |                                   | 2.3.2                                                                                | Soft Real-Time System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                                                                                                                                 |

|   | 2.4                               | Fault                                                                                | Hypothesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 13                                                                                                                                 |

|   |                                   | 2.4.1                                                                                | Fault-Containment Regions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13                                                                                                                                 |

|   |                                   | 2.4.2                                                                                | Failure Mode Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14                                                                                                                                 |

|   |                                   | 2.4.3                                                                                | Failure Rate Assumptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15                                                                                                                                 |

|   |                                   | 2.4.4                                                                                | Recovery Interval of an FCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                 |

|   |                                   | 2.4.5                                                                                | Maximum Number of Failures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15                                                                                                                                 |

|   | 2.5                               | Partiti                                                                              | oning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                                                                                                 |

|   |                                   | 2.5.1                                                                                | Temporal Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                                                                                                 |

|   |                                   | 2.5.2                                                                                | Spatial Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 16                                                                                                                                 |

|   | 2.6                               | Fault a                                                                              | and Error Containment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17                                                                                                                                 |

|   |                                   | 2.6.1                                                                                | Fault Containment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                                                                                 |

|   |                                   | 2.6.2                                                                                | Error Containment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 17                                                                                                                                 |

|   |                                   |                                                                                      | 2.6.2.1 Within computing node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17                                                                                                                                 |

|   | 2.7                               | Comm                                                                                 | nunication Mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17                                                                                                                                 |

|   |                                   | 2.7.1                                                                                | Shared-memory based Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                                                                                                                                 |

|   |                                   | 2.7.2                                                                                | Message-based Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                                                                                                                                 |

|   | 2.8                               | System                                                                               | n Reconfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                                                                                                                                 |

| 3 | Dala                              | ated Wo                                                                              | 1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21                                                                                                                                 |

| 3 | Kela                              | ited wi                                                                              | JIK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>41</b>                                                                                                                          |

|   | 21                                | Pool T                                                                               | ima Operating System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 21                                                                                                                                 |

|   | 3.1                               |                                                                                      | 1 0 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21<br>21                                                                                                                           |

|   | 3.1                               | Real-7<br>3.1.1                                                                      | RTOS Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21                                                                                                                                 |

|   | 3.1                               |                                                                                      | RTOS Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21<br>21                                                                                                                           |

|   | 3.1                               | 3.1.1                                                                                | RTOS Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21<br>21<br>22                                                                                                                     |

|   | 3.1                               |                                                                                      | RTOS Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21<br>21<br>22<br>22                                                                                                               |

|   | 3.1                               | 3.1.1                                                                                | RTOS Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21<br>21<br>22<br>22<br>22                                                                                                         |

|   |                                   | 3.1.1<br>3.1.2                                                                       | RTOS Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21<br>21<br>22<br>22<br>22<br>23                                                                                                   |

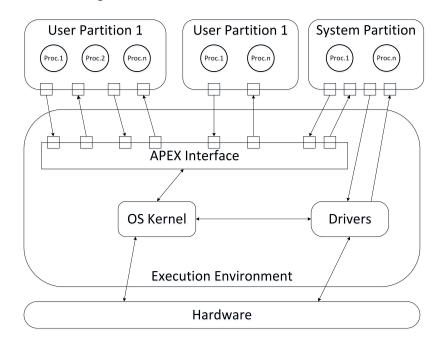

|   | <ul><li>3.1</li><li>3.2</li></ul> | 3.1.1<br>3.1.2<br>ARIN                                                               | RTOS Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ol> <li>21</li> <li>21</li> <li>22</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> </ol>                                     |

|   |                                   | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1                                                      | RTOS Capability    3.1.1.1 Memory Management    3.1.1.1 Memory Management      3.1.1.2 Scheduling    3.1.2.2 Scheduling    3.1.2.1 PikeOS      3.1.2.1 PikeOS    3.1.2.2 Linux RTAI/LXRT    3.1.2.2 Scheduling      C 653    59stem Architecture    59stem Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>21</li> <li>21</li> <li>22</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>24</li> </ul>                         |

|   |                                   | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2                                             | RTOS Capability       3.1.1.1         Memory Management       3.1.1.2         Scheduling       3.1.1.2         Related Work on RTOS       3.1.2.1         PikeOS       3.1.2.2         Linux RTAI/LXRT       3.1.2.2         System Architecture       3.1.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21<br>21<br>22<br>22<br>23<br>23<br>23<br>24<br>24                                                                                 |

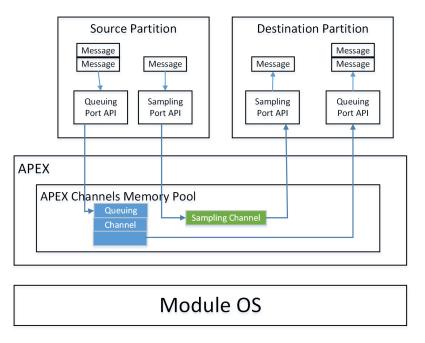

|   |                                   | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1                                                      | RTOS Capability       3.1.1.1 Memory Management         3.1.1.1 Memory Management       3.1.1.2 Scheduling         3.1.1.2 Scheduling       3.1.2.1 PikeOS         3.1.2.1 PikeOS       3.1.2.2 Linux RTAI/LXRT         3.1.2.2 Linux RTAI/LXRT       3.1.2.2 C653         System Architecture       3.1.2.1 PikeOS         Communication Mechanism       3.1.2.1 PikeOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <ul> <li>21</li> <li>21</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>24</li> <li>24</li> <li>25</li> </ul>             |

|   |                                   | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2                                             | RTOS Capability       3.1.1.1 Memory Management         3.1.1.1 Memory Management       3.1.1.2 Scheduling         3.1.1.2 Scheduling       3.1.2.1 PikeOS         3.1.2.1 PikeOS       3.1.2.2 Linux RTAI/LXRT         3.1.2.2 Linux RTAI/LXRT       3.1.2.2 C653         System Architecture       3.1.2.1 PikeOS         System Architecture       3.1.2.1 PikeOS </td <td>21<br/>21<br/>22<br/>22<br/>23<br/>23<br/>23<br/>24<br/>24<br/>25<br/>25</td> | 21<br>21<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>25<br>25                                                                     |

|   |                                   | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2<br>3.2.3                                    | RTOS Capability       3.1.1.1 Memory Management         3.1.1.2 Scheduling       3.1.2.2 Scheduling         Related Work on RTOS       3.1.2.1 PikeOS         3.1.2.1 PikeOS       3.1.2.2 Linux RTAI/LXRT         3.1.2.2 Linux RTAI/LXRT       3.1.2.2 System Architecture         Partitioning       3.1.2.1 PikeOS         System Architecture       3.1.2.1 PikeOS                                                                                     | <ul> <li>21</li> <li>21</li> <li>22</li> <li>22</li> <li>23</li> <li>23</li> <li>24</li> <li>25</li> <li>25</li> <li>26</li> </ul> |

|   |                                   | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4                           | RTOS Capability3.1.1.1Memory Management3.1.1.2Scheduling3.1.2.1Scheduling3.1.2.1PikeOS3.1.2.2Linux RTAI/LXRTC 653System ArchitecturePartitioningSector3.2.3.1Inter-partition Communication3.2.3.2Intra-partition CommunicationSystem ReconfigurationSystem Reconfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 21<br>21<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>25<br>25<br>26<br>27                                                         |

|   | 3.2                               | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5                  | RTOS Capability3.1.1.1Memory Management3.1.1.2Scheduling3.1.1.2SchedulingRelated Work on RTOS3.1.2.1PikeOS3.1.2.2Linux RTAI/LXRTC 653System ArchitecturePartitioningCommunication Mechanism3.2.3.1Inter-partition Communication3.2.3.2Intra-partition CommunicationSystem ReconfigurationResearch Gap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21<br>21<br>22<br>22<br>23<br>23<br>23<br>24<br>25<br>25<br>25<br>26<br>27<br>27                                                   |

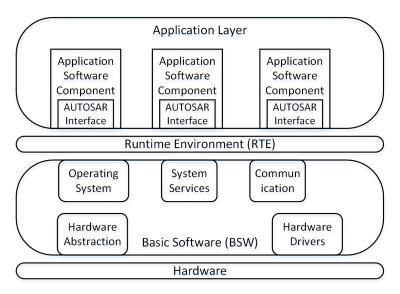

|   |                                   | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>AUTC          | RTOS Capability3.1.1.1Memory Management3.1.1.2SchedulingRelated Work on RTOS3.1.2.1PikeOS3.1.2.2Linux RTAI/LXRTC 653System ArchitecturePartitioningCommunication Mechanism3.2.3.1Inter-partition CommunicationSystem ReconfigurationSystem ReconfigurationSAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21<br>21<br>22<br>22<br>23<br>23<br>24<br>25<br>25<br>26<br>27<br>27<br>27                                                         |

|   | 3.2                               | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>AUTC<br>3.3.1 | RTOS Capability3.1.1.1Memory Management3.1.1.2SchedulingRelated Work on RTOS3.1.2.1PikeOS3.1.2.2Linux RTAI/LXRTC 653System ArchitecturePartitioningCommunication Mechanism3.2.3.1Inter-partition CommunicationSystem ReconfigurationSystem ReconfigurationSARSystem Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 21<br>21<br>22<br>22<br>23<br>23<br>23<br>24<br>24<br>25<br>25<br>26<br>27<br>27<br>27<br>27                                       |

|   | 3.2                               | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>AUTC          | RTOS Capability3.1.1.1Memory Management3.1.1.2SchedulingRelated Work on RTOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21<br>21<br>22<br>22<br>23<br>23<br>24<br>25<br>25<br>26<br>27<br>27<br>27<br>27<br>28                                             |

|   | 3.2                               | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>AUTC<br>3.3.1 | RTOS Capability3.1.1.1Memory Management3.1.1.2SchedulingRelated Work on RTOS3.1.2.1PikeOS3.1.2.2Linux RTAI/LXRTC 653System ArchitecturePartitioningCommunication Mechanism3.2.3.1Inter-partition Communication3.2.3.2Intra-partition CommunicationSystem ReconfigurationResearch GapSystem ArchitectureSystem ArchitectureSystem Architecture3.2.3.1Inter-partition Communication3.2.3.2Intra-partition CommunicationSystem ReconfigurationSystem ArchitectureSystem ArchitectureSystem ArchitectureSystem ArchitectureSupport ArchitectureSystem ArchitectureSystem ArchitectureSupport ArchitectureSup                                                                                                                                                                                                                                                                                 | 21<br>21<br>22<br>22<br>23<br>23<br>24<br>24<br>25<br>25<br>26<br>27<br>27<br>27<br>27<br>28<br>28                                 |

|   | 3.2                               | 3.1.1<br>3.1.2<br>ARIN<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>AUTC<br>3.3.1 | RTOS Capability3.1.1.1Memory Management3.1.1.2SchedulingRelated Work on RTOS3.1.2.1PikeOS3.1.2.2Linux RTAI/LXRTC 653System ArchitecturePartitioningCommunication Mechanism3.2.3.1Inter-partition Communication3.2.3.2Intra-partition CommunicationSystem ReconfigurationSystem ArchitectureSystem ReconfigurationSystem ArchitectureSystem ArchitectureSystem ReconfigurationSystem ArchitectureSystem ArchitectureSala.1Client/Server Paradigm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21<br>21<br>22<br>22<br>23<br>23<br>24<br>24<br>25<br>25<br>26<br>27<br>27<br>27<br>27<br>28<br>28<br>29                           |

|   |     | 3.3.4                                                                                  | System                                                                                                                                                                                                    | Reconfiguration                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                                                                                                                             |

|---|-----|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |     | 3.3.5                                                                                  | Research                                                                                                                                                                                                  | n Gap                                                                                                                                                                                                                                                                                                                                                                               | 30                                                                                                                                                                                             |

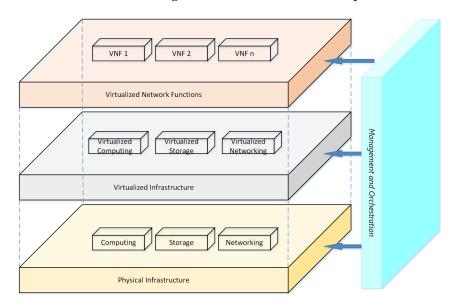

|   | 3.4 | Virtua                                                                                 | l Networ                                                                                                                                                                                                  | king                                                                                                                                                                                                                                                                                                                                                                                | 31                                                                                                                                                                                             |

|   |     | 3.4.1                                                                                  | History                                                                                                                                                                                                   | of Network Virtualization                                                                                                                                                                                                                                                                                                                                                           | 31                                                                                                                                                                                             |