# Distributed Co-Simulation Framework for Hardware- and Software-In-The-Loop Testing of Networked Embedded Real-Time Systems

#### DISSERTATION

zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften

vorgelegt von Tobias Pieper, M. Sc.

eingereicht bei der Naturwissenschaftlich-Technischen Fakultät der Universität Siegen Siegen 2020

# Betreuer und erster Gutachter Prof. Dr. Roman Obermaisser Universität Siegen

Zweiter Gutachter

Prof. Dr. Uwe Brinkschulte

Johann Wolfgang Goethe-Universität Frankfurt

Vorsitzender der Promotionskommission Prof. Dr. Kristof Van Laerhoven Universität Siegen

Tag der mündlichen Prüfung: 05.10.2020

### **Abstract**

Today's complex control systems such as trains, aircraft or cars are typically composed of multiple networked components which are developed by geographically distributed manufacturers. During their development process, integrating and testing the components are central steps. However, the manufacturers' locations complicate the process since the components must be shipped to a central place and intellectual property must be protected. Using a distributed co-simulation framework which supports Software- and Hardware-In-The-Loop (SIL/HIL) testing can solve these issues. It enables a virtual integration and testing of the components via the Internet and protects intellectual property if it operates on a network-centric abstraction level. In this case, it focuses on the data exchange between the components and knowledge about their internal implementation is not required.

In today's state-of-the-art, a framework that operates on a network-centric abstraction level and supports co-simulation, SIL and HIL testing together is not available yet. Besides that, HIL testing involves hardware devices with real-time requirements. Connecting those devices via public wide area networks such as the Internet, the accuracy of distributed HIL tests is limited by the determinism of the network's communication delays. The available frameworks are mainly based on Quality of Service mechanisms such as differentiated services. However, the communication cycles of the System Under Test (SUT) might be smaller than the guaranteed latencies which leads to deadline misses. Hence, delay-management mechanisms are required which ensure a timely forwarding of input data.

This thesis proposes a distributed co-simulation framework which operates on a network-centric abstraction level and supports the above mentioned techniques. It synchronizes the components of the SUT, coordinates their data exchange and includes fault-injection to validate the dependability. By providing a generic component interface, heterogeneous simulation tools and physical devices are supported. The main contributions of the thesis are two delay-management mechanisms based on state-estimation and speculative execution. The first mechanism forwards estimated inputs to the component if (I) received inputs are delayed or (II) as intermediary inputs. This reduces the number of communication activities inside the framework. The second mechanism divides a simulation setup

into several subsets. Those subsets execute independent tasks in advance to forward data to real-time devices in time. Using the mechanisms, the framework is able to connect simulations, software algorithms and real hardware via public communication networks while maintaining the SUT's real-time requirements. Hence, there is no need to make all simulation models or physical prototypes centrally available.

The evaluation using a distributed control application demonstrates the scalability of the framework. The time to execute a simulation setup increases linearly with the simulated time and is bounded by the growth of the component's number in larger setups. Furthermore, the evaluation shows the advantages of the delay-management mechanisms for distributed real-time tests. After determining a proper real-time configuration of the simulation host, the state-estimation mechanism can be used for a timely forwarding of inputs to the components. Using intermediary packets improves the accuracy of distributed real-time tests and makes it independent from the network delays. While the speculative execution enables real-time tests locally and in Local Area Networks, networks with larger delays (e.g., the Internet) require less stringent temporal requirements of the SUT. From a performance point of view, both mechanisms achieve significant speedups depending on the setup's size, the network topology and the communication period.

# Zusammenfassung

Heutige komplexe Steuerungssysteme wie Züge, Flugzeuge oder Autos bestehen in der Regel aus mehreren vernetzten Komponenten, die von geografisch verteilten Herstellern entwickelt werden. Während ihres Entwicklungsprozesses sind die Integration und das Testen der Komponenten zentrale Schritte. Die Standorte der Hersteller erschweren jedoch den Prozess, da die Komponenten an einen Ort geliefert werden müssen und Intellectual Property geschützt werden muss. Die Verwendung eines verteilten Co-Simulations-Frameworks, das Software- und Hardware-in-the-Loop (SIL/HIL) Tests unterstützt, kann diese Probleme lösen. Es ermöglicht eine virtuelle Integration sowie das Testen der Komponenten über das Internet und schützt Intellectual Property, wenn es auf einer netzwerkzentrischen Abstraktionsebene arbeitet. In diesem Fall konzentriert es sich auf den Datenaustausch zwischen den Komponenten und Kenntnisse über ihre interne Implementierung sind nicht erforderlich.

Nach dem heutigen Stand der Technik ist ein Framework, das auf einer netzwerkzentrischen Abstraktionsebene arbeitet und Co-Simulation, SIL- und HIL-Tests unterstützt, noch nicht verfügbar. Außerdem werden beim HIL-Test Hardware-Geräte mit Echtzeitanforderungen eingesetzt. Wenn diese Geräte über öffentliche Wide Area Networks wie das Internet miteinander verbunden werden, ist die Genauigkeit verteilter HIL-Tests durch den Determinismus der Netzwerklatenzen begrenzt. Die verfügbaren Frameworks basieren hauptsächlich auf Quality of Service Mechanismen wie z.B. Differentiated Services. Die Kommunikationszyklen des Systems Under Test (SUT) können jedoch kleiner als die garantierten Latenzen sein, was zu Deadline-Überschreitungen führt. Daher sind Mechanismen zur Verwaltung von Verzögerungen erforderlich, die eine rechtzeitige Weiterleitung der Eingangspakete gewährleisten.

Diese Dissertation schlägt ein verteiltes Co-Simulations-Framework vor, das auf einer netzwerkzentrischen Abstraktionsebene arbeitet und die oben genannten Techniken unterstützt. Es synchronisiert die Komponenten des SUT, koordiniert ihren Datenaustausch und beinhaltet Fehlerinjektionsmechanismen zur Validierung der Zuverlässigkeit. Durch die Bereitstellung einer generischen Komponentenschnittstelle werden heterogene Simulationswerkzeuge und physikalische Geräte unterstützt. Die wichtigsten Beiträge

dieser Dissertation sind zwei Mechanismen zur Verwaltung von Verzögerungen, die auf State-Estimation und spekulativer Ausführung basieren. Der erste Mechanismus leitet vorhergesagte Pakete an die Komponente weiter, wenn (I) empfangene Pakete verzögert werden oder (II) als zusätzliche Pakete zwischen den Empfangenen. Dadurch wird der Nachrichtenaustausch innerhalb des Frameworks reduziert. Der zweite Mechanismus teilt die Simulation in mehrere Untergruppen auf. Diese Untergruppen führen unabhängige Tasks im Voraus aus, um Daten rechtzeitig an Echtzeitgeräte weiterzuleiten. Mit Hilfe der Mechanismen ist das Framework in der Lage, Simulationen, Software-Algorithmen und reale Hardware über öffentliche Kommunikationsnetze zu verbinden und gleichzeitig die Echtzeitanforderungen des SUTs zu erfüllen. Es ist daher nicht notwendig, alle Simulationsmodelle oder physikalische Prototypen zentral zur Verfügung zu stellen.

Die Auswertung mit einer verteilten Steuerungsanwendung demonstriert die Skalierbarkeit des Frameworks. Die Zeit für die Ausführung einer Simulation steigt linear mit der simulierten Zeit und ist durch das Wachstum der Anzahl der Komponenten in größeren Setups begrenzt. Darüber hinaus zeigt die Auswertung die Vorteile des Verzögerungsmanagements für verteilte Echtzeittests. Nach der Bestimmung einer geeigneten Echtzeitkonfiguration des Simulations-PCs kann der State-Estimation-Mechanismus für eine rechtzeitige Weiterleitung von Paketen an die Komponenten verwendet werden. Die Verwendung von zusätzlichen Paketen zwischen den Empfangenen verbessert die Genauigkeit von verteilten Echtzeittests und macht sie unabhängig von den Verzögerungen im Netzwerk. Während die spekulative Ausführung Echtzeittests lokal und in Local Area Networks ermöglicht, erfordern Netzwerke mit größeren Verzögerungen (z.B. das Internet) weniger strikte zeitliche Anforderungen an das SUT. Aus Performance-Sicht erreichen beide Mechanismen je nach Größe des Setups, der Netzwerktopologie und der Kommunikationsperiode erhebliche Speedups.

# **Danksagung**

Diese Dissertation wurde während meiner Arbeit als Wissenschaftlicher Mitarbeiter am Lehrstuhl Embedded Systems der Universität Siegen erstellt. Die Grundlagen hierzu entstanden im Rahmen des europäischen Forschungsprojekts Safe4RAIL, welches durch das Horizon 2020 Programms für Forschung und Innovation der Europäischen Union unter Grant Agreement Nummer 730830 gefördert wurde.

Zuerst möchte ich mich ausdrücklich beim Inhaber des Lehrstuhls Embedded Systems, Professor Dr. Roman Obermaisser, bedanken. Dieser Dank gilt besonders für die Betreuung der Dissertation, die Anstellung als Wissenschaftlicher Mitarbeiter sowie das Vertrauen, mir die Leitung des Arbeitspakets Virtual Placement in the Market des Safe4-RAIL Projekts zu übertragen. Des Weiteren möchte ich mich bei Professor Dr. Uwe Brinkschulte für die Erstellung des Zweitgutachtens bedanken. Professor Dr. Kristof Van Laerhoven danke ich für die Leitung des Promotionsverfahren und Professor Dr. Roland Wismüller für seine Funktion als weiterer Prüfer.

Ein weiterer großer Dank gilt meinen Kollegen am Lehrstuhl Embedded Systems. Besonders bedanken möchte ich mich bei Hongjie Fang, Daniel Onwuchekwa und Maryam Pahlevan für die umfangreichen und regelmäßigen Diskussionen im Rahmen des Safe4-RAIL Projekts sowie bei Michael Schmidt für unsere gemeinsame Forschung über Echtzeit-Linux und seine Nutzung für Mixed-Criticality Systeme. Diese Forschung hat die Echtzeitkonfiguration der PCs erst möglich gemacht. Des Weiteren danke ich Stefan Otterbach für die Anschaffung und Bereitstellung der notwendigen Hard- und Software sowie allen Kollegen für die vielen fachlichen und persönlichen Gespräche. Darüber hinaus danke ich allen Partnern des Safe4RAIL Projekts für die vielen fachlichen Diskussionen und die gute Zusammenarbeit im Arbeitspaket.

Dr. Regina Fuchs danke ich aus zweierlei Hinsicht. Einerseits für das Korrekturlesen der Dissertation, andererseits für die vielen Stunden, die wir während meines Studiums an der Entwicklung einer Mess- und Regeleinrichtung für Adhäsionsmessungen mittels Nanoindenter gearbeitet haben. Während dieser Zeit konnte ich eine Menge an praktischer Erfahrung sammeln und sie hat maßgeblich zu der Entscheidung beigetragen, ein

Promotionsstudium zu absolvieren.

Abschließend bedanke ich mich bei meiner Familie und meinen Freunden für jegliche Unterstützung und Motivation, vor allem in Zeiten von Zweifel, schlechter Laune und Motivationslosigkeit. Ohne diese Unterstützung hätte ich mich niemals voll auf das Studium und die Promotion konzentrieren können. Vielen Dank!

# **Contents**

| Lis | t of  | Figure  | s                                      | XIII |

|-----|-------|---------|----------------------------------------|------|

| Lis | st of | Tables  |                                        | XVI  |

| Ac  | rony  | ms      | 2                                      | XVII |

| 1   | Intr  | oductio | on                                     | 1    |

|     | 1.1   | Motiv   | ration                                 | . 1  |

|     | 1.2   | Objec   | etives and Contribution of this Thesis | . 3  |

|     | 1.3   | Outlin  | ne                                     | . 5  |

| 2   | Fun   | damen   | tals                                   | 7    |

|     | 2.1   | Real-   | Γime Systems                           | . 7  |

|     |       | 2.1.1   | Characteristics of Real-Time Systems   | . 7  |

|     |       | 2.1.2   | Time and Clock Synchronization         | . 9  |

|     |       | 2.1.3   | Composability                          | . 12 |

|     |       | 2.1.4   | Determinism                            | . 15 |

|     |       | 2.1.5   | Real-Time Communication                | . 16 |

|     |       | 2.1.6   | Real-Time Operating Systems            | . 18 |

|     |       | 2.1.7   | Temporal Accuracy and State-Estimation | . 21 |

|     | 2.2   | System  | m Design and Validation                | . 22 |

|     |       | 2.2.1   | Design of Real-Time Systems            | . 22 |

|     |       | 2.2.2   | Verification and Validation            | . 23 |

|     | 2.3   | Distri  | buted Co-Simulation                    | . 25 |

|     | 2.4   | Softwa  | are- and Hardware-In-The-Loop Testing  | . 28 |

|     | 2.5   | Fault-  | Injection                              | . 29 |

|     | 2.6   | Comn    | nunication and Data Security           | . 31 |

| 3   | Rela  | ated W  | /ork                                   | 33   |

|     | 3.1   | Real-   | Γime Communication Systems             | . 33 |

|     |       | 3 1 1   | TTEthernet                             | 33   |

|   |      | 3.1.2   | Time Sensitive Networking                                          | 34      |

|---|------|---------|--------------------------------------------------------------------|---------|

|   | 3.2  | Distrib | outed Co-Simulation                                                | 35      |

|   |      | 3.2.1   | Distributed Co-Simulation Frameworks                               | 35      |

|   |      | 3.2.2   | The Functional Mock-Up Interface                                   | 37      |

|   |      | 3.2.3   | The High Level Architecture                                        | 38      |

|   |      | 3.2.4   | Combinations of FMI and HLA                                        | 40      |

|   | 3.3  | Softwa  | are- and Hardware-In-The-Loop Testing                              | 40      |

|   | 3.4  | Linux   | as Real-Time Operating System                                      | 42      |

|   | 3.5  | Techno  | ologies for Real-Time Tests via the Internet                       | 44      |

|   |      | 3.5.1   | Quality of Service Protocols for the Internet                      | 45      |

|   |      | 3.5.2   | State-Estimation                                                   | 46      |

|   |      | 3.5.3   | Speculative Execution                                              | 47      |

|   | 3.6  | Netwo   | rk-Centric Fault-Injection Tools                                   | 47      |

|   | 3.7  | Securi  | ty Mechanisms                                                      | 49      |

|   | 3.8  | Resear  | rch Gap                                                            | 49      |

| _ |      |         |                                                                    |         |

| 4 |      | work-C  | entric Distributed Co-Simulation Framework supporting HIL and      |         |

|   | SIL  | 4 3 4   |                                                                    | 53      |

|   | 4.1  |         | sectural Overview of the Framework                                 | 53      |

|   |      | 4.1.1   | Overall Architecture                                               | 53      |

|   |      | 4.1.2   | Functionality of Simulation Bridges                                | 57      |

|   | 4.2  | _       | guration and Simulation Execution                                  | 60      |

|   | 4.3  |         | Synchronization                                                    | 64      |

|   |      | 4.3.1   | Time Management in the High Level Architecture                     |         |

|   |      | 4.3.2   | Synchronization of Simulation Bridges                              |         |

|   |      | 4.3.3   | Synchronization in Real-Time                                       | 70      |

|   | 4.4  |         | t Handling in the Simulation Bridges                               | 73      |

|   | 4.5  |         | Injection based on IEC 61508-2                                     | 75      |

|   | 4.6  |         | are- and Hardware-In-The-Loop Testing                              | 77      |

|   | 4.7  | Secure  | e Communication                                                    | 78      |

| 5 | Dela | av-Man  | agement in Distributed Real-Time Tests via the Internet            | 79      |

| • | 5.1  | •       | Management using State-Estimation                                  | 79      |

|   | 0.1  | 5.1.1   | State-Estimation Models                                            | 79      |

|   |      | 5.1.2   | State-Estimation as Fall-Back Solution for Timely Packet Reception | 80      |

|   |      | 5.1.3   | Increased Accuracy using Estimated Intermediary Packets            | 83      |

|   | 5.2  |         | Management using Speculative Execution                             | 87      |

|   | IJ.∠ |         | Concept of Speculative Execution                                   |         |

|   |      | U.4.1   | COHCODU OI DICCHIAUIYO LIACCUUIOH                                  | $\circ$ |

|    |       | 5.2.2    | Extending Simulation Bridges to Simulation Gateways               | . 90  |

|----|-------|----------|-------------------------------------------------------------------|-------|

| 6  | Eval  | luation  | using a Fault-Tolerant Fan-Control Application                    | 95    |

|    | 6.1   | System   | n Under Test for Framework Evaluation                             | . 95  |

|    |       | 6.1.1    | Fan-Control Application                                           | . 95  |

|    |       | 6.1.2    | FMUs of Fan, PID Controllers and Voter                            | . 101 |

|    |       | 6.1.3    | Implementation of Fan on Zynq-XC7Z010 Hardware                    | . 104 |

|    | 6.2   | Imple    | mentation of the Distributed Co-Simulation Framework on Linux .   | . 107 |

|    |       | 6.2.1    | Implementation of Simulation Bridges                              | . 108 |

|    |       | 6.2.2    | Configuration of Linux as Real-Time Host                          | . 109 |

|    | 6.3   | Influer  | nce of Fault-Injection on Fan-Control                             | . 113 |

|    |       | 6.3.1    | Fault-Injection in SIL Testing                                    | . 113 |

|    |       | 6.3.2    | Fault-Injection in HIL Testing                                    | . 116 |

|    | 6.4   | Frame    | work Scalability                                                  | . 123 |

|    |       | 6.4.1    | Synchronization Data Exchange                                     | . 124 |

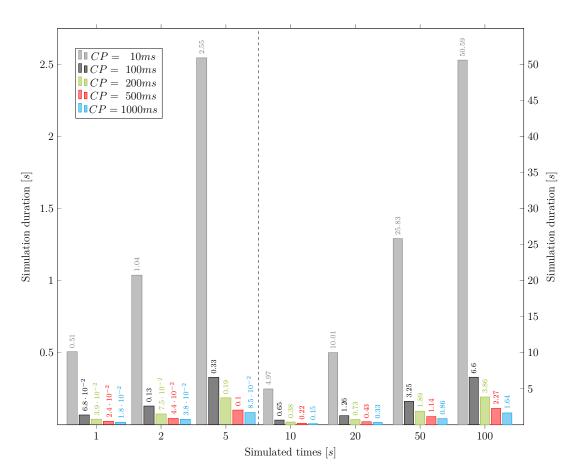

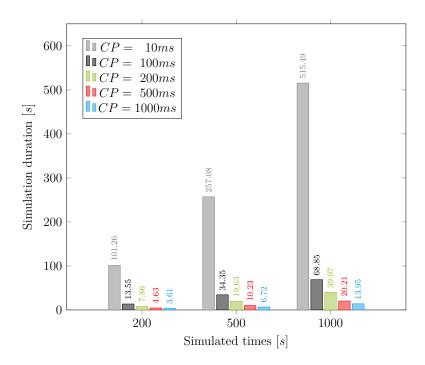

|    |       | 6.4.2    | Simulation Runtime and Simulated Time                             | . 127 |

|    | 6.5   | Qualit   | y Improvement of Distributed Co-Simulation using State-Estimation | 132   |

|    |       | 6.5.1    | Timely Packet Reception for Real-Time Devices                     | . 132 |

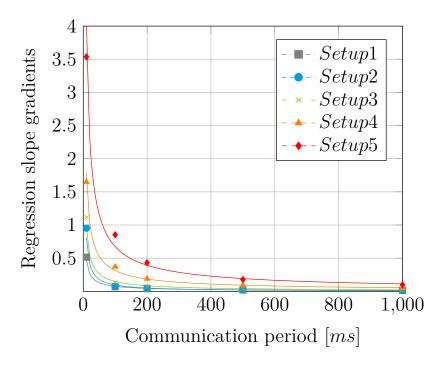

|    |       | 6.5.2    | Performance Speedup using State-Estimation                        | . 135 |

|    | 6.6   | Perfor   | mance Speedup using Speculative Execution                         | . 140 |

| 7  | Con   | clusion  | and Future Work                                                   | 145   |

|    | 7.1   | Summ     | ary and Contribution                                              | . 145 |

|    | 7.2   | Future   | e Work                                                            | . 147 |

| Α  | Con   | figurati | ion Model                                                         | 151   |

| В  | Syn   | chroniz  | ation Messages                                                    | 155   |

| C  | Sim   | ulation  | Durations without Delay-Management                                | 157   |

| D  | Spe   | edup U   | sing State-Estimation                                             | 159   |

| E  | Spe   | edup U   | sing Speculative Execution                                        | 165   |

| F  | Pub   | lication | ns and Copyright Information                                      | 171   |

| Re | ferer | ices     |                                                                   | 173   |

# **List of Figures**

| 2.1  | Periodic resynchronization with regard to [KO87]                         | 11 |

|------|--------------------------------------------------------------------------|----|

| 2.2  | Sparse time-base (adapted from [KAGS05, Kop07])                          | 12 |

| 2.3  | Connected clusters (adapted from [Obe11, p. 7], [Kop11, p. 81])          | 13 |

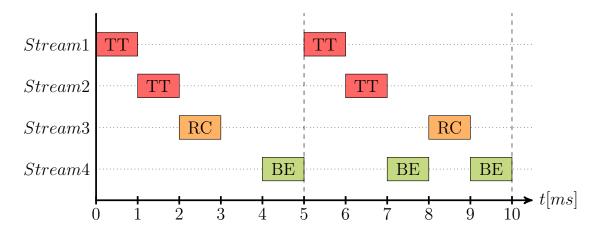

| 2.4  | TDMA with time-triggered, rate-constrained and best-effort data streams. | 17 |

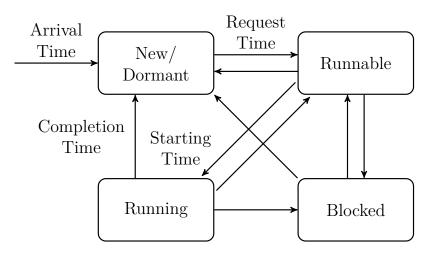

| 2.5  | Task states and temporal parameters (adapted from [WB05, p. 352])        | 19 |

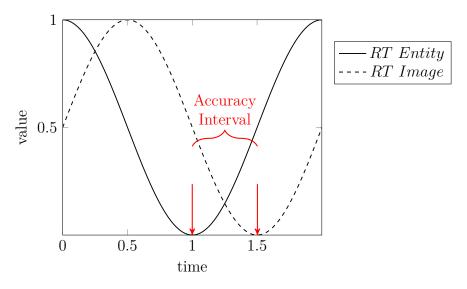

| 2.6  | Temporal delay and accuracy interval (adapted from [Kop11, p. 117])      | 21 |

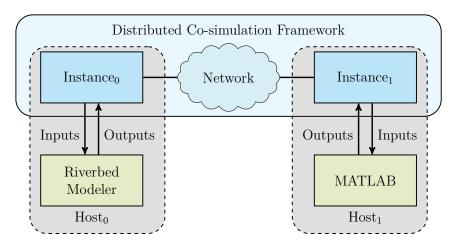

| 2.7  | Co-simulation framework                                                  | 26 |

| 2.8  | Distributed co-simulation framework via a communication network          | 27 |

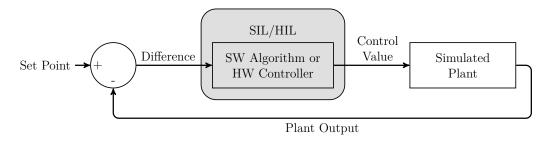

| 2.9  | Software- and Hardware-In-The-Loop testing                               | 29 |

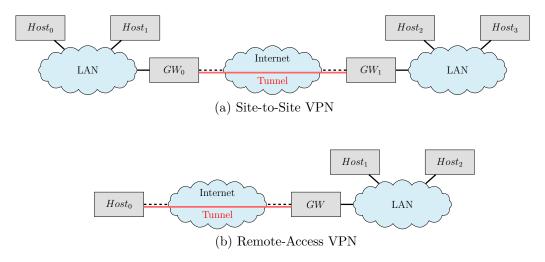

| 2.10 | Different types of VPNs                                                  | 32 |

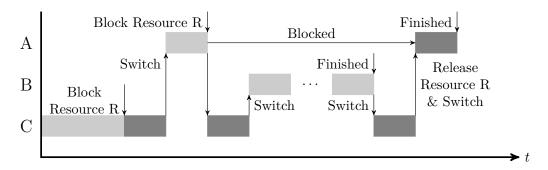

| 3.1  | Priority Inversion (adapted from [WB05, p. 390])                         | 43 |

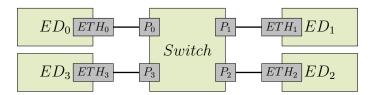

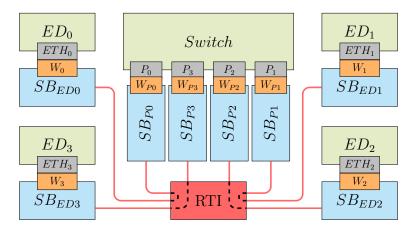

| 4.1  | Distributed SUT using Ethernet                                           | 54 |

| 4.2  | Connecting the subsystems of an SUT using the distributed co-simulation  |    |

|      | framework                                                                | 54 |

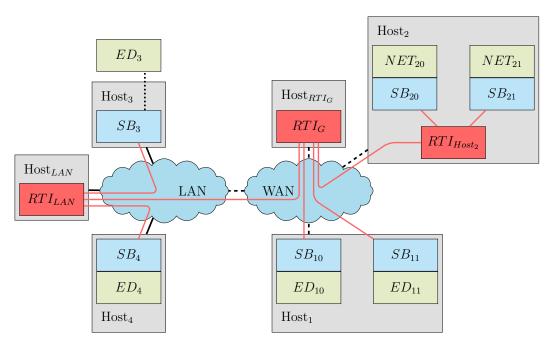

| 4.3  | Possible topology of the distributed co-simulation framework             | 56 |

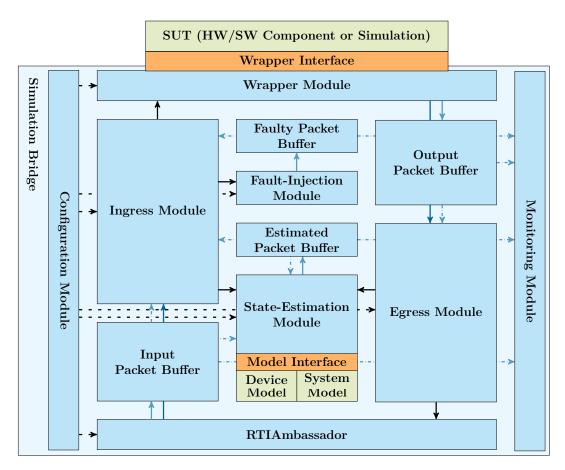

| 4.4  | Architecture of simulation bridges                                       | 57 |

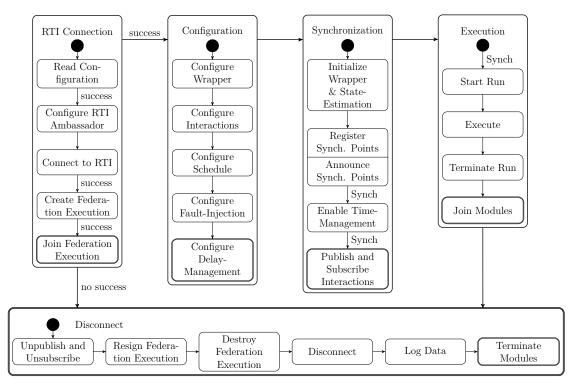

| 4.5  | Simulation bridge configuration and simulation execution                 | 61 |

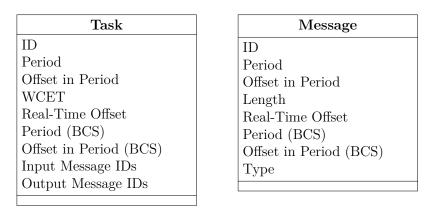

| 4.6  | Parameters of tasks and messages                                         | 61 |

| 4.7  | Initial step in the time management algorithm                            | 66 |

| 4.8  | First step in the algorithm, time advance of $ED_0$                      | 66 |

| 4.9  | Time advance of $NET$ as the second step                                 | 67 |

| 4.10 | Third step showing the time advance of $ED_1$                            | 67 |

| 4.11 | Fourth step in the time management algorithm, time advance of $NET.$     | 67 |

| 4.12 | Fifth step with time advance of $ED_0$                                   | 68 |

| 4.13 | Main loop in the ingress module                                          | 69 |

| 5.1  | Communication delays causing a retarded execution of a real-time task    | 82 |

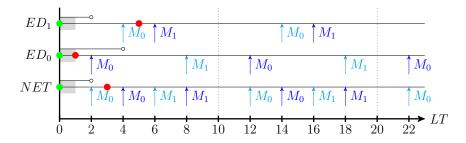

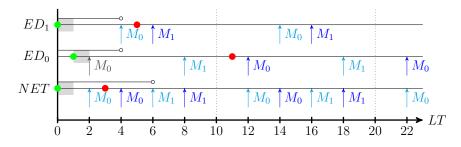

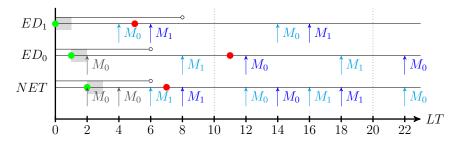

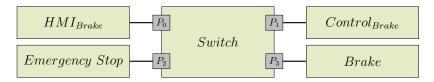

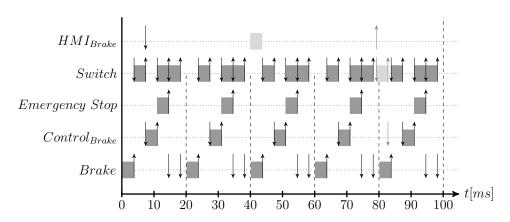

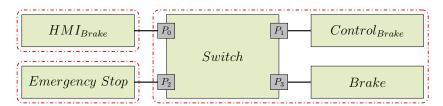

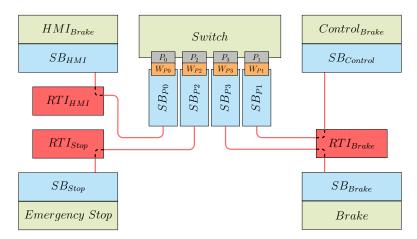

| 5.2  | Dense application schedule of two end devices connected via a switch     | 83 |

| 5.3  | Definition of events in bridge communication schedule                    | 84 |

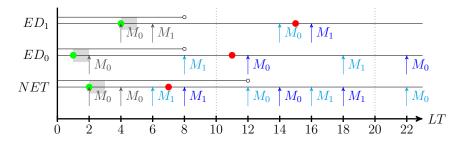

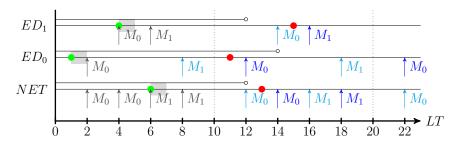

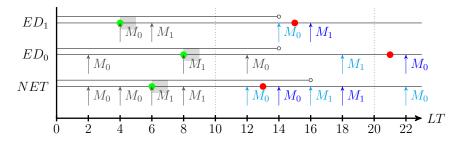

| 5.4  | Application of state-estimation providing intermediary packets 85                      |

|------|----------------------------------------------------------------------------------------|

| 5.5  | Distributed SUT with different cycle times                                             |

| 5.6  | Schedule of example SUT                                                                |

| 5.7  | Different subsets of SUT                                                               |

| 5.8  | Connecting the subsystems of the SUT using simulation bridges 89                       |

| 5.9  | Adapted schedule of example SUT with early execution of independent tasks. 90          |

| 5.10 | Architecture of simulation gateways                                                    |

| 5.11 | Local and global event schedules                                                       |

| 6.1  | Fan control application without redundancy                                             |

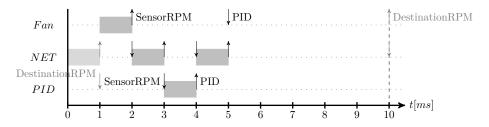

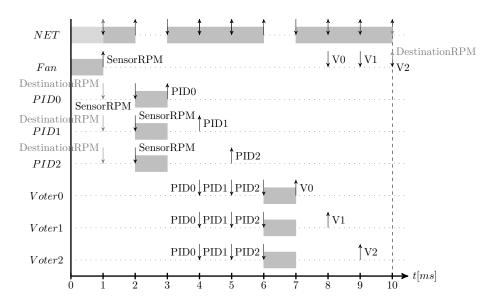

| 6.2  | Schedules in DUT without redundancy for one period of 10ms 96                          |

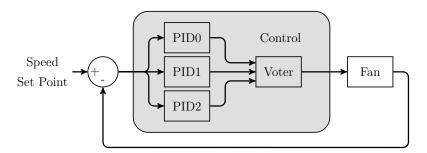

| 6.3  | Fan control application with triplicated PID controller                                |

| 6.4  | Schedule in DUT with triplicated PID controller for one period of 10ms 97              |

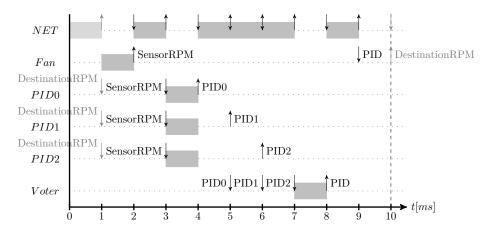

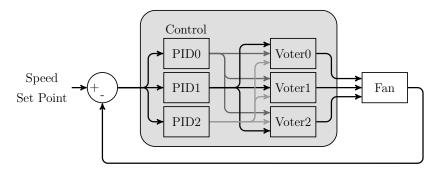

| 6.5  | Fan control application with triplicated PID controller and voter 98                   |

| 6.6  | Schedule in DUT with triplicated PID controller and voter                              |

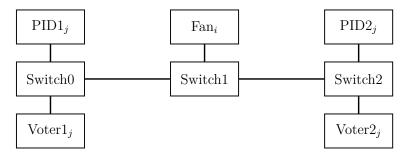

| 6.7  | Duplicated fan control application based on Setup 3                                    |

| 6.8  | Schedule of duplicated fan control application                                         |

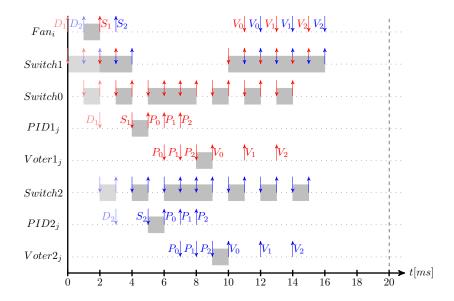

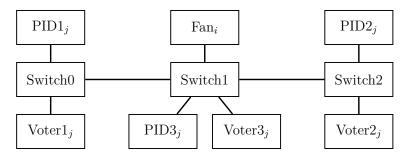

| 6.9  | Triplicated fan control application based on Setup 3                                   |

| 6.10 | Schedule of triplicated fan control application                                        |

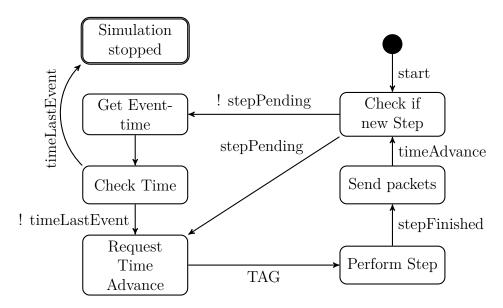

| 6.11 | Execution control thread                                                               |

| 6.12 | Fan control thread                                                                     |

| 6.13 | Topology to demonstrate the fault-injection mechanism in a SIL test. $$ 113            |

| 6.14 | Fan speed during normal execution, corruption, delay and insertion $115$               |

| 6.15 | Fan speed during normal execution, omission, resequencing and replay. $$ . $$ . $$ 116 |

| 6.16 | Topology to demonstrate the fault-injection mechanism in a HIL test $117$              |

| 6.17 | Packet capture with corruption error                                                   |

| 6.18 | Packet capture with delay error                                                        |

| 6.19 | Packet capture with insertion error                                                    |

| 6.20 | Wireshark packet captures with replay error                                            |

| 6.21 | Packet capture with resequencing error                                                 |

| 6.22 | Packet capture with omission error                                                     |

| 6.23 | $\rm HIL$ fan speed during normal execution, corruption, delay and insertion $122$     |

| 6.24 | HIL fan speed during normal execution, omission, resequencing and replay. 123          |

| 6.25 | Time advance in sparse schedule                                                        |

| 6.26 | Different topologies used during the evaluation based on Setup 1 128                   |

| 6.27 | Simulation durations for SIL in a local topology                                       |

| 6.28 | Simulation durations for SIL in a LAN setup                                            |

| 6.29 | Simulation durations for SIL in a setup with communication via the Internet.130        |

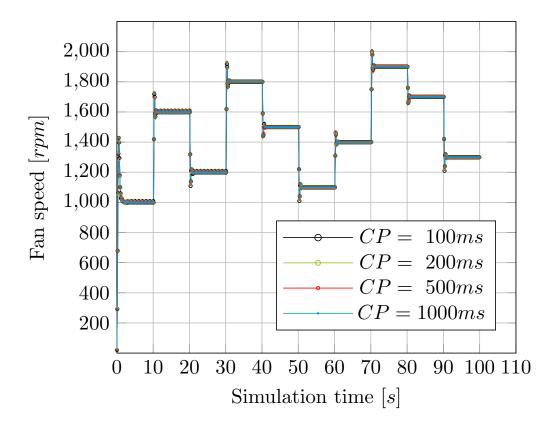

| 0.30 | Fan speed without state-estimation and increasing communication periods. 133 |

|------|------------------------------------------------------------------------------|

| 6.31 | State-estimation enabled to guarantee a timely packet reception              |

| 6.32 | State-estimation enabled to forward intermediary packets                     |

| 6.33 | Speedup using state-estimation for Setup 1 (1s to 100s)                      |

| 6.34 | Speedup using state-estimation for Setup 1 (200s to 1000s)                   |

| 6.35 | Speedup using state-estimation in the local topology                         |

| 6.36 | Speedup using state-estimation in a LAN                                      |

| 6.37 | Speedup using state-estimation via the Internet                              |

| 6.38 | Subsets of Setup 3                                                           |

| 6.39 | Subsets of Setup 5                                                           |

| 6.40 | Speedup for Setup 5 using speculative execution (200s to 1000s) 141          |

| 6.41 | Speedup for Setup 5 using speculative execution (1s to 100s)                 |

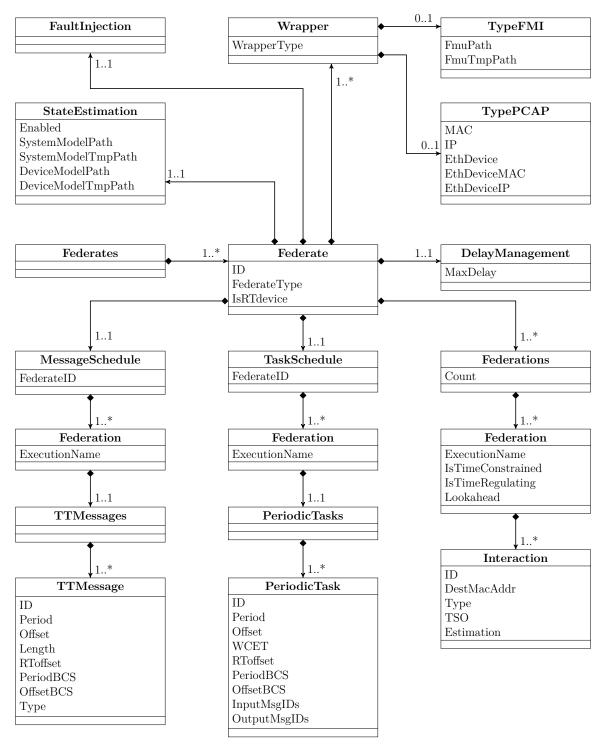

| A.1  | Main elements of the configuration file                                      |

|      | Attributes of the federations                                                |

| A.3  |                                                                              |

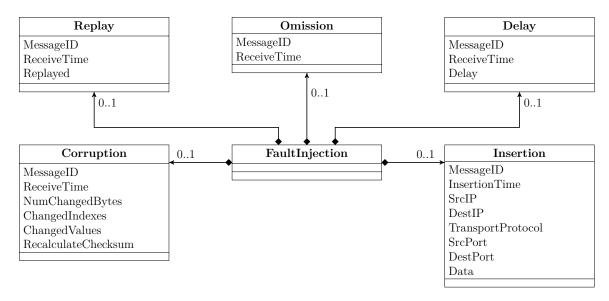

| A.4  | Attributes of error modes for the fault-injection                            |

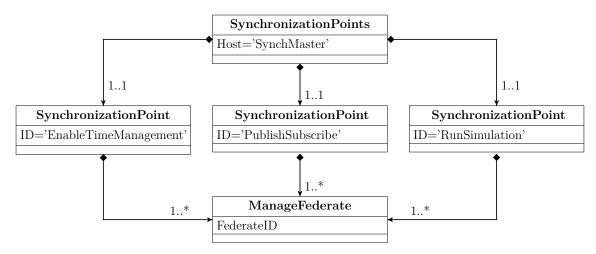

| A.5  | Attributes of synchronization points                                         |

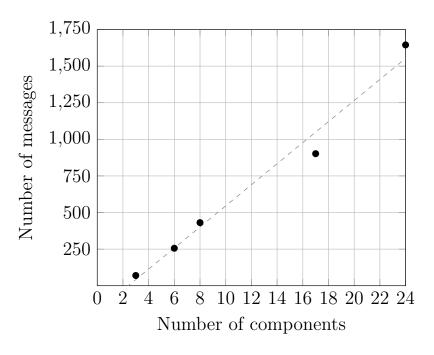

| B 1  | Number of synchronization data messages per period 155                       |

# **List of Tables**

| 4.1  | Configuration parameters of message errors                               |

|------|--------------------------------------------------------------------------|

| 6.1  | Configuration of real-time host in different test cases                  |

| 6.2  | Missed events and packet loss                                            |

| 6.3  | Duration of ingress and egress threads and ingress scheduling delays 112 |

| 6.4  | Configuration of message errors                                          |

| 6.5  | Configuration of message errors                                          |

| 6.6  | Numbers and sets of synchronization data exchange                        |

| 6.7  | Number of events and messages per period in the different setups 127     |

| 6.8  | Correlation between slopes of average runtime, number of components and  |

|      | number of messages                                                       |

| 6.9  | Achievable speedups for a communication period of $500ms$ 139            |

| 6.10 | Speedups for local and LAN topologies                                    |

| 6.11 | Speedups for distributed simulations via the Internet                    |

| В.1  | Number of messages for a simulated time of 1s                            |

| C.1  | Simulation durations and deviations for Setup 1                          |

| C.2  | Simulation durations and deviations for Setup 2                          |

| С.3  | Simulation durations and deviations for Setup 3                          |

| C.4  | Simulation durations and deviations for Setup 4                          |

| C.5  | Simulation durations and deviations for Setup 5                          |

| D.1  | Regression slopes of Setups 1, 2 and 3 for the different topologies and  |

|      | communication periods                                                    |

| D.2  | Local and LAN regression slopes of Setups 4 and 5 for different communi- |

|      | cation periods                                                           |

| D.3  | Power functions for regression of speedups                               |

| D.4  | Simulation durations and deviations for Setup 1                          |

| D.5  | Simulation durations and deviations for Setup 2                          |

| D.6  | Simulation durations and deviations for Setup 3                          |

| D.7 | Simulation durations and deviations for Setup 4                      |

|-----|----------------------------------------------------------------------|

| D.8 | Simulation durations and deviations for Setup 5                      |

|     |                                                                      |

| E.1 | Simulation durations and deviations for Setup 1 (Local and LAN) 165  |

| E.2 | Simulation durations and deviations for Setup 1 via the Internet 165 |

| E.3 | Simulation durations and deviations for Setup 2 (Local and LAN) 166  |

| E.4 | Simulation durations and deviations for Setup 2 via the Internet 166 |

| E.5 | Simulation durations and deviations for Setup 3 (Local and LAN) 167  |

| E.6 | Simulation durations and deviations for Setup 3 via the Internet 167 |

| E.7 | Simulation durations and deviations for Setup 4                      |

| E.8 | Simulation durations and deviations for Setup 5                      |

# **Acronyms**

**AVB** Audio/Video Bridging

**DetNet** Deterministic Networking

**DiffServ** Differentiated Services

**ETB** Ethernet Train Backbone

**ECN** Ethernet Consist Network

**ECU** Electronic Control Unit

FCR Fault-Containment Region

FMI Functional Mock-up Interface

FMU Functional Mock-up Unit

**GALT** Greatest Available Logical Time

**HIL** Hardware-In-The-Loop

**HLA** High Level Architecture

**HMI** Human Machine Interface

**HVAC** Heating, Ventilation and Air Conditioning

**IntServ** Integrated Services

LAN Local Area Network

**MPLS** Multiprotocol Label Switching

MTTF Mean Time To Failure

**OMT** Object Model Template

**PID** Proportional, Integral and Derivative

**PTP** Precision Time Protocol

**PWM** Pulse Width Modulation

**QoS** Quality of Service

**RSVP** Resource Reservation Protocol

**RTAI** Real-Time Application Interface

**RTI** Runtime Infrastruture

**RTOS** Real-Time Operating System

**SIL** Software-In-The-Loop

**STL** Standard Template Library

**SUT** System Under Test

**TDMA** Time Division Multiple Access

**TSN** Time Sensitive Networking

**TSO** Timestamped Order

TMR Triple Modular Redundancy

**VPN** Virtual Private Network

**V&V** Verification and Validation

**WCET** Worst-Case Execution Time

**WCCOM** Worst-Case Communication Delay

# 1. Introduction

#### 1.1. Motivation

Nowadays, embedded systems can be found almost everywhere: in transportation, factory automation, smart buildings or grids, robotics and in health care [Mar18, p. 4ff.]. In 2011, about 98% of all microprocessors were embedded. Using sensors and actuators, they are able to interact with their environment and the connection via communication networks establishes large-scale distributed embedded real-time systems [aca11, p.5]. Typical examples of such complex systems are aircrafts [SP13], trains [JGSJS18] or a modern car. The latter can contain 100 connected Electronic Control Units (ECUs) which control several physical processes [WCAF15].

Typically, the connected control systems are developed by several, geographically distributed manufacturers. For trains as an example, the German ASC GmbH and Frauscher Sensortechnik GmbH provide different types of sensors, the Interautomation Deutschland GmbH concentrates on passenger WiFi or infotainment, Knorr-Bremse develops braking systems and the Konvekta AG is supplier for Heating, Ventilation and Air Conditioning (HVAC) systems [Int19]. Besides them, UniControls a.s. from the Czech Republic provides network units or I/O systems. Regarding the automotive domain, examples of suppliers are Robert Bosch GmbH (e.g., electronics), Denso Corp. (e.g., powertrain control), Continental AG (e.g., advanced driver assistance), Infineon Technologies AG (e.g., micro-controllers) or Brose Fahrzeugteile GmbH (e.g., mechatronic systems) [Cha18].

During the development process, the components are designed separately, integrated once they are available and tested afterwards. The final system is built incrementally by repeating the steps [BST10, p. 233-236]. In this process, verification and validation are major steps, which are even more important if the system under test is safety-critical. Common examples of such systems are trains, aircrafts and parts of a car. Without a valid safety argument, human life might be endangered while using those systems [SMS<sup>+</sup>13]. Besides this, validating a system early in the development process prevents issues in later stages [BCPS11]. However, the distributed locations of the different suppliers complicate

the process. To integrate and validate the components, they must be shipped to a central place which introduces costs and causes delays. Furthermore, intellectual property must be protected [HLV06].

Using techniques such as distributed co-simulation, Software- and Hardware-In-The-Loop (SIL, HIL) testing can simplify the development process. They are common technologies which enable a repeatable and controllable component testing. Since many simulation tools are developed for dedicated purposes (e.g., Riverbed Modeler for communication networks and MATLAB for controlled plants), they are coupled to co-simulate complex systems [CDF<sup>+</sup>14]. Coupling them via the Internet or Local Area Networks (LANs), it is further possible to connect geographically distributed tools. In SIL testing, models of control algorithms are replaced by their software implementation and validated against models of the rest of the system [BCPS11]. This technology supports an early identification of design faults. Furthermore, physical prototypes are not yet required which results in less costs and no risk of damage or accidents [BVP10]. The validation of physical system components is performed in HIL testing instead. If the tested hardware is a real-time device, its temporal requirements must also be satisfied during the validation process. In a setup distributed via the Internet, the network's best effort character introduces indeterministic communication delays into the test system. While there are no consequences on a System Under Test (SUT) without any real-time components (e.g., SIL setups), the delays might lead to deadline misses in real-time components of a HIL test. Hence, delaymanagement mechanisms are required which (I) detect the delays and stop the test and (II) cope with the unpredictability of the communication. Finally, fault-injection during HIL and SIL testing allows to investigate a system's behavior in case of faults. Since the injection can be performed in a deterministic way, it is a widely used and effective validation technique.

The difficulties caused by the manufacturers' distributed locations can be addressed if the systems under test are integrated via time-triggered real-time communication networks. In such networks, the instants of all communication activities are a priori known [EBK03]. Using the instants as events in a co-simulation helps to synchronize the time advance of distributed simulations. Furthermore, instants for message reception denote the deadlines for real-time hardware at which the packets have to be delivered. With this knowledge, it is possible to mitigate delays in the test system.

This thesis introduces a framework which validates the component integration on a network-centric abstraction level. Since it focuses on the data exchange via the linking network interfaces, the components' internal implementations need not be known during the integration and validation process. By distributing the framework across LANs and

the Internet, the components can be validated at their manufacturers' sites during early development steps. In this way, shipping and integrating the components at a central place is not required and intellectual property can be protected. Furthermore, it facilitates the interplay between the manufacturers which expedites the development process and reduces costs.

As shown in this thesis, there is a lack of generic, network-centric frameworks which cover the entire validation process including co-simulation, SIL and HIL testing. If they do so, they suffer from suitable delay-management technologies which enable real-time tests via the Internet or do not consider the injection of faults.

#### 1.2. Objectives and Contribution of this Thesis

The framework developed in this thesis aims on validating the behavior of subsystems in time-triggered networked control systems. Those systems are common for safety-critical domains such as avionics, railway or automotive, but can be found also in other areas. Their safety-critical character introduces research objectives which can be grouped into five different categories. They are defined in the following.

Distributed Co-Simulation Framework The first objective is the development of a cosimulation framework which is distributed via heterogeneous communication networks such as LANs or the Internet. In this way, it is possible to connect simulations between geographically distributed locations, for example between sites of

different manufacturers. The distributed character and the transmission of potentially confidential data requires the inclusion of suitable security mechanisms. To

validate the communication between the components, the framework operates on a

network-centric abstraction level. Hence, the data exchanged between the simulations are the packets sent via the components' network interfaces. Using a scalable

synchronization mechanism, the data exchange and the time advance of the simulations need to be coordinated in the correct temporal order. At last, the framework

shall provide a generic interface to connect a large number of simulation tools.

Software- and Hardware-In-The-Loop testing Simulations are replaced gradually by software applications and the real hardware during the development process. Hence, the developed framework shall support Software- and Hardware-In-The-Loop testing. The latter involves the execution in real-time wherefore the framework must ensure a timely data exchange and the synchronization of the logical simulation time and the physical time of the components in the HIL test. Furthermore, an interface

is required which is able to capture and forward network traffic.

**Real-time simulation hosts** Connecting real hardware requires a communication between the framework and the devices in real-time. Hence, also the connected simulation hosts on which the framework is running have to provide real-time guarantees. In this way, the packets can be forwarded to the hardware in time.

Delay-management for distributed real-time tests In addition to real-time execution of the simulation host, the data transfer inside the framework must be performed in time. However, heterogeneous communication networks such as the Internet introduce indeterministic communication jitter and packet loss. Even if QoS mechanisms are applied, it is not able to provide the level of determinism required by safety-critical applications. The distributed co-simulation framework shall provide mechanisms which cope with delays leading to deadline misses as follows: (I) a detection mechanism which stops the simulation and (II) mechanisms which ensure a timely input reception for real-time devices.

Fault-injection support Fault-injection is an effective way to validate the behavior of a system in the case of faults. Failures in components of a distributed SUT typically propagate to other subsystems via faulty messages. Hence, the framework shall support a mechanism to inject faults into the communication between the subsystems of the SUT. In this way, failures of the components can be mapped to the communication network. Since the communication may be safety-critical, the injection has to follow related standards.

Within this thesis, a distributed co-simulation framework is proposed which covers all these objectives. It operates on a network-centric abstraction level and supports Software-and Hardware-In-The-Loop testing. Furthermore, a fault-injection mechanism is included which covers all message errors defined in clause 7.4.11 of part two of the IEC 61508 standard for Functional safety of electrical/electronic/programmable electronic safety-related systems [iec11]. Using the standard, the faults are injected directly into the packets exchanged. The main contributions of this thesis are three delay-management technologies which ensure real-time testing via the Internet. The first approach uses state-estimation as a fall-back solution for a timely packet reception. By estimating intermediary packets, the second approach forwards packets to the components in time independent from the framework's communication delays. Finally, a third mechanism distributes the ensemble of components into subsets so that independent processes can execute speculatively in advance. In this way, Internet-introduced delays can be mitigated to maintain the deadlines in hard real-time devices.

#### 1.3. Outline

The remainder of this thesis is organized as follows.

- Chapter 2 starts with an overview about basic knowledge regarding topics covered in this work. At first, it denotes the characteristics of distributed real-time systems as the SUTs for which the distributed co-simulation framework is developed. Afterwards, an overview about a typical development and validation process is given followed by example technologies for validation. Those are distributed co-simulation, SIL and HIL testing and fault-injection. Since the framework exchanges potentially confidential data, the chapter closes with a discussion about available security mechanisms.

- Chapter 3 continues with an analysis of the current state-of-the-art. In addition to related work regarding the topics introduced in the previous chapter, further technologies are presented. Those are mechanisms to transform Linux into a real-time operating system and to realize Quality of Service via the Internet. Additionally, state-estimation mechanisms and speculative execution as alternative delay-management techniques are depicted. Based on the state-of-the-art analysis, the research gap for this work is defined at the end of the chapter.

- Chapter 4 introduces the developed network-centric co-simulation framework. It covers the overall architecture and the simulation bridges as the main components. In the subsequent sections, their functionality is described in detail with regard to SIL and HIL testing. This includes the configuration, synchronization and packet handling mechanisms together with the injection of faults. Finally, the application of VPNs to secure the communication within the framework is explained.

- **Chapter 5** covers the three delay-management techniques developed. Two of these techniques use state-estimation while the third one is based on speculative execution. They target on enabling distributed real-time tests via the Internet.

- **Chapter 6** focuses on the evaluation of the distributed co-simulation framework and the delay-management mechanisms. Before evaluation results are presented, a suitable configuration for a real-time Linux simulation host is determined. Furthermore, a fault-tolerant and scalable fan-control application is introduced as the SUT.

- **Chapter 7** concludes the thesis. In addition to a summary of the main contributions, it depicts potential aspects for future work.

# 2. Fundamentals

#### 2.1. Real-Time Systems

There are several characteristics of distributed real-time systems the developed framework grounds on. This includes time and the synchronization of clocks, composability, component-based design and determinism. Besides this, real-time communication, real-time operating systems and the property of temporal accuracy are important aspects. All of them are introduced in the following.

#### 2.1.1. Characteristics of Real-Time Systems

In real-time systems, the correctness of a task does not only depend on the correctness of the logical result, but also on its availability at a defined point in time [Sch05, p.40]. This point in time is called a deadline. If it is not met, there are different consequences depending on the type of the real-time system. There are soft, firm and hard deadlines. For soft deadlines, the result may be useful even if the deadline is missed. If the result looses its usefulness instead, the deadline is called firm. When missing a deadline results in catastrophic consequences on the system's environment, the deadline is called hard [Kop98b].

According to the above definitions, real-time systems can be classified as two types. Systems without any hard deadline are called soft real-time systems. If there is at least one hard deadline that has to be met, we speak about hard or safety-critical real-time systems. The latter have to guarantee a temporal behavior in all specified load and fault conditions [Kop11, p.3]. Hence, determinism is a very important aspect during design and test. Examples for soft and hard real-time systems are video and audio streaming where missing a deadline only results in reduced quality (soft), and the flight control system in an aircraft (hard) [Sch05, p.40]. If this system fails in meeting the deadline, it might cause the aircraft to crash. Hence, it is classified as a hard real-time system.

Computer systems may not provide their correct functionality throughout the entire operation. Avizienis et al. [ALRL04] provide a detailed overview about the reasons for those deviations and the resulting consequences in their paper. Typically, a fault causes an error in the state of the system. Categories of faults are for example development and operational faults, software and hardware faults, or natural and human-made ones. If the error causes the system's provided service to deviate from the specified one, one speaks about a failure of the system. Those failures can be classified in their domain (temporal, content), detectability, consistency or in their consequences. Without any countermeasures, a failure might propagate causing a fault in another subsystem. This may continue the chain and cause further errors and failures.

The concepts of faults, errors and failures are covered in dependability which includes reliability, maintainability, availability, safety and security [Mar06, p.2]. The first aspect, reliability, describes the probability that a system will not fail over a defined period of time under specified environmental conditions [Mul85]. If a failure occurs, maintainability represents the time interval which is required to repair the system. Both aspects influence the availability of a system. It is defined as the temporal fraction the system provides its service [ALR+01]. If the reliability is low, the system fails often and must be repaired. Similarly, the system cannot be used if it takes much time to repair it after a failure occurred. Standards such as DO-178C [do111], IEC 61508 [iec10] or ISO 26262 [ISO11] group critical failures into dedicated categories, for example the Safety Integrity Levels 1-4 in IEC 61508. The reliability against those modes is considered as the safety of a system [ALR+01]. Finally, security covers the aspects of confidentiality, integrity and authenticity of data. It is important to consider them, because faults could be introduced intentionally [ALRL04]. For example, the message errors listed in IEC 61508-2 clause 7.4.11 might be caused by malicious components or users.

Handling failures is an important requirement in safety-critical systems. Those systems are used for safety-critical purposes having a direct impact on their controlled environment [Mar06, p.2]. The associated Mean Time To Failure (MTTF) accounts to better than  $10^9h$  [LH94]. Since normal hardware can achieve only an order of  $10^4h$  up to  $10^5h$ , fault-tolerance mechanisms are required [Kop11, p.272]. They use additional information (e.g., parity bits) or redundant hardware and software which detect and correct errors and failures [Sch05, p.182]. To realize this, the redundant components can be grouped into so-called Fault Containment Regions (FCRs). Those regions are defined as correctly operating subsystems unconcerned from any external fault. Using FCRs can prevent the propagation of faults to components outside the region, but the faults can manifest as erroneous data which is propagated. Hence, redundant FCRs are required to realize error containment [LH94]. A widely used concept is Triple Modular Redundancy (TMR). Here,

a component is triplicated and a voting mechanism determines the correct value [LV62]. The tolerated faults of a system are defined in the fault hypothesis [HS95]. Faults that are not covered require a so-called never-give-up strategy which brings the system back into a safe state [Kop11, p.154]. Systems where such a state can be reached upon the occurrence of a failure are called fail-safe. However, there are systems like the flight control of an aircraft where safe states are impossible. Those systems must be fail-operational and provide a minimum level of service to prevent a catastrophe [KKS<sup>+</sup>15].

Internally, the execution of tasks and the communication with other systems is initiated by two different control mechanisms. The first type is called event-triggered. Events are state changes in the controlled object or activities within the computer system. One example is the completion of a task [Obe11, p.20]. If such an event occurs, the CPU is activated by an interrupt and has to schedule the task which handles the event. This requires a dynamic scheduling mechanism [Kop11, p.17]. Event-triggered systems exclude events caused by the progress of time. The control mechanism based on this type of events is called time-triggered. Each task or communication activity is released by a predefined tick of a global clock. In a distributed real-time system, this requires a synchronized, global time [Kop98b]. Typically, time-triggered activities repeat periodically [EBK03].

The delay-management technologies developed in this thesis (cf. Chapter 5) concentrate on time-triggered systems. Without delay-management, event-triggered systems are also supported (cf. Chapter 4).

#### 2.1.2. Time and Clock Synchronization

According to [Kop92], real-time can be modeled by a dense and totally ordered set of instants which are arranged on an directed time-line. In an ordered set, two instants p and r occur either simultaneously or mutually precede each other. To call the ordered set dense, there must be at least one instant q between p and r which is not equal to r.

The interval between the instants p and r is called duration. In real-time systems, events occur at instants of the time-line without having a duration [Kop07]. Since there is no order relation between events arising at the same instant, an event set is only partially ordered [Lam78]. To order them, their delivery and causal order are of interest. The latter is used in a sequence of alarms to identify the primary event. It is more than the temporal order since an event  $e_1$  must not be the reason for an event  $e_2$  which happens later. Otherwise, the temporal order is required since the subsequent event  $e_2$  cannot be the cause of  $e_1$  [Kop92]. The delivery order is not related to time and causality. It ensures only the same perceived order of a set of events between all nodes in a distributed

system [Kop11, p. 53].

Time in real-time systems is measured using physical, digital clocks. They contain a counter which increments based on a periodic event. This event is caused by an oscillation mechanism and is called a micro-tick. An important characteristic of a clock is its granularity which is the duration between two successive micro-ticks. In time measurements, the granularity leads to a digitalization error wherefore it must be small. Measuring its value is only possible with a clock having a finer granularity. This can be reached with reference clocks. These clocks typically have a very small granularity and they are perfectly aligned with the international time standard. At runtime, an observer queries the state of the counter to create a time-stamp once an event occurs. They can be used to measure time intervals or to order events [Kop07].

Oscillators differ in quality and price wherefore clocks drift apart [KAH04]. The value of the clock drift represents the frequency ratio between a clock and its reference. It can be calculated by dividing the granularity of the clock z by the number of micro-ticks  $n^k$  in the reference clock during this interval. Subtracting the drift by one and taking the amount provides the drift rate  $\rho$  (cf. Equation 2.1). A perfect drift rate of 0 is impossible, but it can be bounded by a maximum rate. This value typically lies in the order of magnitude of  $10^{-2}$  to  $10^{-7}$ , but it can also be less if better oscillators are used [Kop11, p. 54f.].

$$\rho_i^k = \left| \frac{z(microtick_{i+1}^k) - z(microtick_i^k)}{n^k} - 1 \right|$$

(2.1)

Since every clock has a different drift rate, an ensemble of clocks must be synchronized. There are two possibilities to reach this. In internal synchronization, the precision of the clocks in the ensemble is bounded while external synchronization reduces the accuracy between a clock and a reference [KO87]. Both values are based on the offset between two clocks. It is determined using a reference clock which takes the time-stamps of one of the clocks' respective micro-ticks. The amount of their difference represents the offset. In a set of clocks, the precision denotes the maximum offset between all pairs of clocks during an interval of interest. Similarly, the accuracy represents the maximum offset with regard to the reference clock [Kop11, p. 56].

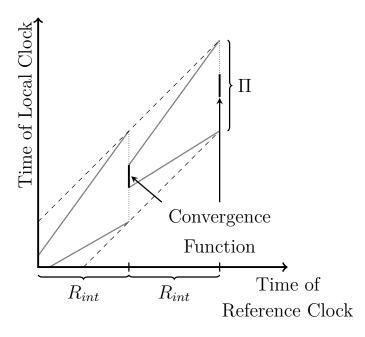

As clock drift arises continuously, internal synchronization must be repeated periodically after an interval  $R_{int}$ . This process is shown in Figure 2.1. The resulting offset at the end of the resynchronization is represented by the convergence function  $\Phi$  while the drift offset  $\Gamma$  denotes the maximum deviation of two clocks. It depends on the specified drift rates of both clocks and the resynchronization interval. The synchronization mechanism must ensure that the sum of the convergence function and the drift offset is always smaller

than the precision  $\Pi$ . Otherwise, a clock will leave the interval [KO87]. The convergence function further defines the correction of the clocks. State-correction adapts the current time value of a clock but leads to discontinuities in the time-base. Rate-correction prevents this issue as the clock speed is adjusted either by adapting the number of micro-ticks per macro-tick or by changing the oscillator voltage [Kop11, p. 72f.]. This mechanism can also be used in external synchronization. A time gateway receives the current time from an external server periodically and adjusts the other clocks in the system [KKMS95].

Figure 2.1.: Periodic resynchronization with regard to [KO87].

In distributed real-time systems, most nodes have an oscillator. Since it is not possible to synchronize those clocks perfectly, the notion of a global time was introduced. It is an approximated abstraction which uses selected micro-ticks of an internally synchronized clock set of precision Π. These ticks are called macro-ticks and the nodes use them to create a local implementation of the global time. The best achievable synchronization error is defined by the reasonableness condition. It bounds the maximum difference between global time-stamps of an event by at most one tick and the synchronization error by less than the granularity of a macro-tick [Kop98a]. As a consequence, it is not possible to reconstruct the temporal order of two events whose global time-stamps differ by one tick. To reconstruct them, the time-stamps must differ by at least two ticks and the clocks must satisfy the reasonableness condition. Furthermore, the true duration of an interval is bounded by the observed duration plus/minus twice the granularity of the global time. Only reducing the global time's granularity can improve this fundamental limitation [Kop11, p. 59f.].

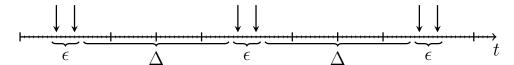

The limitation explained before grounds in the usage of a dense time base. Here, events are entitled to occur at every instant of the time-line [Kop92]. However, it is possible to restrict their occurrence to active intervals of duration  $\epsilon$  which have an interval of silence denoted as  $\Delta$  in between. The resulting sparse time base is shown in Figure 2.2. Events in the same  $\epsilon$ -interval are considered to occur simultaneously. Hence, a consistent temporal order can be reconstructed if the events occur in consecutive  $\epsilon$ -intervals [Kop07] and  $\Delta$  is greater than three times the granularity [Kop95]. The architecture must ensure that significant events (e.g., sending a message or observing the environment) occur only in  $\epsilon$ -intervals. Otherwise, an agreement protocol must be used which requires additional resources (e.g., time, bandwidth, etc.) [KAGS05]. Another benefit of the  $\Delta$ -intervals is the possibility to identify the state of the system clearly. The state represents all values of variables, etc. and separates future activities from the past [Kop11, p. 85]. During the  $\Delta$ -intervals, there are no activities performed and the state can be determined. Using a sparse time base is one central aspect to reach determinism in distributed real-time systems [Kop07]. Since determinism in replicated components enables fault-tolerance, composability is introduced in the following.

Figure 2.2.: Sparse time-base (adapted from [KAGS05, Kop07]).

#### 2.1.3. Composability

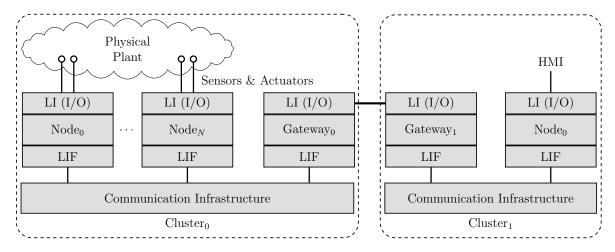

Large systems can be built from prefabricated components that are connected via standardized interfaces. In this way, knowledge about a component's internal design or implementation is not required as long as the component's behavior at the interface is correct [Kop98a]. In real-time systems, the temporal correctness is as important as the correctness of computational results. Since there is no possibility to assign temporal capabilities to a software, it requires a virtual or real hardware unit for execution [Obe11, p. 28]. Figure 2.3 illustrates an example system which consists of two connected clusters, a physical plant and a Human Machine Interface (HMI). The different components and interfaces are introduced in the following.

In distributed computer systems, a component must be separated from the communication infrastructure. This infrastructure provides a unidirectional message exchange from a sending component as unicast (one receiver) or multicast (multiple receivers) during a defined time-interval. Since the message transfer is unidirectional, error propagation from

a faulty receiver to a correct sender is avoided. This property is very important in fault-tolerant systems, similar to multicasting [Kop11, p. 80f.]. Multicasting supports a timely correct reception of a single message by multiple receivers. This is required for active redundancy and fault-tolerance [KAGS05].

Figure 2.3.: Connected clusters (adapted from [Obe11, p. 7], [Kop11, p. 81]).

Messages exchanged via the communication infrastructure consist of a header, a data field and a trailer. The header contains delivery information like the destination address or how the message has to be handled. Besides this, the data field contains the message's content. Each message has to be delivered in its whole. Since the trailer contains checksums or electronic signatures, a corruption and the authenticity of the message can be checked. If it is not received completely or the trailer does not match, it is discarded. The transport delay of a message is given by the time interval between the instants for sending and receiving it. To prevent congestion of the receiver, it is possible to constrain the rate messages are sent with [Kop11, p. 88f.]. This is realized using the so called minimum inter-arrival time which has to elapse before another message instance can follow [AOA16].

A message can be either time-triggered or event-triggered. The latter type is sent with regard to an event that occurred in the system. It contains information about this event and it is unique, wherefore a receiver must process all messages to determine the new state [Kop99]. Error detection can only be performed by the sender as the receiver does not know whether an event occurred. Hence, it requires an explicit acknowledgement. As the sender must decide whether the transmission failed within a defined real-time interval, fault-tolerant systems cannot be built on systems that are not aware of the progression of real-time [Kop11, p. 91]. In contrast, time-triggered messages are sent periodically at a defined point in time and contain information about the system's state [KS03]. Using the temporal knowledge, congestion can be avoided and the receiver is able to detect errors. If the receive instant elapsed without any reception, a failure occurred in the sender or

the message is lost in the communication infrastructure [Kop11, p. 91].

There are four types of interfaces that components provide [Kop11, p. 92]:

- 1. Linking Interface (LIF)

- 2. Technology-Independent Control Interface (TICI)

- 3. Technology-Dependent Debug Interface (TDDI)

- 4. Local Interface (LI)

The linking interface provides the specified service and connects the component to other components building a cluster (cf. Figure 2.3). It is message-based and must be independent from the internal implementation of the component. Otherwise, it is not possible to develop components independently [Kop02a]. The technology-independent control interface is used to configure and control the component. Arriving messages are handled by the hardware itself or by the operating system, but not by the application. In this way, the application and the overall complexity of the node can be simplified [Kop11, p. 94]. Via the technology-dependent debug interface it is possible to debug the component. It is intended for the component's developer who can observe the state of variables and it is irrelevant for the user [KS03]. Finally, the local interfaces connect the component with its environment [Kop02a] as shown in Figure 2.3. Besides sensors and actuators in the physical plant, this can be a human operator or another computer [Kop11, p. 95].

Components containing a local and a linking interface are called gateway components. At cluster level, only the timing and the semantic content of the local interface are important. Hence, its technology can be exchanged without any influence on the linking interface [Kop11, p. 95f.]. Gateway components link two different systems which may have varying data representations, data semantics or component interactions. Hence, a gateway has to adapt the different technologies used between the systems [Kop98a].

The integration of components into a cluster requires four principles. First, the component shall be developed independently. To reach this, it must define the specification of the linking interface precisely. This covers the interface data structures in the value and time domains and a conceptual interface model of the provided service. Second, the component's LIF must provide the specified service and the integration must not change the functionality. Besides this, the component is not allowed to interfere with communication activities of other components. Finally, a component must be replica deterministic to support fault-tolerance by replication [KO02]. With these principals, it is possible to integrate the components building clusters. Those clusters can be connected further via gateway components to develop large systems [Kop98a].

#### 2.1.4. Determinism

According to Bunge [Bun17, p. 7], a machine is called deterministic if it runs regular and reproducible. As a consequence, determinism enables the prediction of future system states and outputs based on an initial state, the sequence of inputs and the progress of time. With this prediction, it is easier to understand the system's real-time behavior and testing is simplified. In addition, it enables fault-tolerance by replication [Kop08a].

A desired feature in a system with replicated components is replica determinism. If those components start in the same state and receive the same inputs, they produce the same outputs in approximately the same time. Using this property, it is possible to mask failures of a component in a properly designed fault-tolerant system [Kop95]. A failure occurred if one replicated component does not work according to its specification. In this case, the system requires time to correct the failure using the outputs of the correctly working components. How much time it takes must be deduced from the application dynamics and can be bounded by the precision of the global time in time-triggered systems. To ensure the correct behavior, it is important to prevent failures caused by the software. Only random, physical faults are allowed to occur [Obe11, p. 34].

Realizing (replica-)determinism in distributed real-time systems requires several aspects. First, all components must agree on a consistent initial state and they must receive inputs simultaneously [Obe11, p.33]. Similarly, an agreement is required on the inputs of the components. Due to digitalization errors, these inputs might differ in the temporal and value domain [Pol94]. Using a dense time base, events can be observed in a different order which leads to a significantly diverging behavior. A sparse time base prevents these errors and enables the simultaneous provision of inputs to all components [Kop07]. Furthermore, it facilitates the determination of a consistent state [Kop11, p. 128].

The second requirement covers certain computations. This includes arbitrary values such as random numbers or the protection of shared resources via non-deterministic synchronization mechanisms [Pol94]. Those mechanisms should be avoided. The same accounts for preemptive scheduling. Here, a task may be interrupted due to an external event leading to a deadline miss [Kop11, p. 129f.]. Non-preemptive scheduling prevents this issue. If it cannot be used, all possible task preemptions must be considered during the design [Obe11, p.37].

Finally, the instants when messages are delivered should be known. Using a time-triggered communication mechanism, all instants of the message delivery are defined in advance. In addition, the temporal order of all messages equals at sender and receiver and there are no arbitrary delays. Both aspects are further requirements [KAGS05].

#### 2.1.5. Real-Time Communication

Components in real-time embedded systems exchange data via communication networks. The characteristics of real-time systems explained in Section 2.1.1 impose various requirements on those networks. This section presents the requirements and introduces typical traffic types afterwards.

The stability of feedback control loops depends on the time between reading a sensor value and performing an actuation. In networked control systems, this time is influenced by the network delays and their variation [KÖC<sup>+</sup>94] which is called jitter. Another big influence on the control's quality is the precision of the clock synchronization mechanism. Hence, communication delays and jitter should be minimized and the synchronization mechanism must provide a global time base with a proper precision [Kop11, p. 168]. Furthermore, real-time behavior of the communication system and known jitter are required to comply with the deadlines of the system [Kop00].

Further important properties are reliability and determinism. Reliability includes the transmission of messages via replicated communication channels [GK91] and robust encoding with error-detecting or even correcting codes. As retransmission in case of a failure increases the jitter significantly, it should be avoided. However, the communication system should detect the faulty behavior of components and report it [Kop11, p. 168ff.]. In addition, it should prevent the propagation of temporal faults between the components. To realize this, temporal firewalls can be used. They exploit common knowledge about the transmission instants to block faulty messages [Kop98b]. A deterministic message transfer covers a correct message order on all channels and replicated messages must arrive at simultaneous instants [Kop08b].

In distributed real-time systems, the standard communication type is a multicast as the same data is required often by multiple components. One example is fault-tolerance using replication. Hence, the communication network should support this type [GK91]. Due to frequent changes in the configuration, it must be possible to add components dynamically. This must not require changes and retesting of existing ones. Furthermore, a congestion of the available bandwidth must be avoided [Kop11, p. 171].

Communication channels are often shared resources as the amount of costs and weight due to wiring can be reduced. Multiplexing enables the transmission of multiple signals via the same channel [TW11, p. 125]. The technology considered in this thesis is Time Division Multiplexing, also called Time Division Multiple Access (TDMA). Every data stream receives the entire bandwidth periodically for a dedicated amount of time. The streams must be synchronized and small timing variations can be compensated using

guard times [TW11, p. 135]. Time-triggered networks are based on this technology which provides a deterministic transmission, low latency and low jitter. Additionally, different traffic types such as time-triggered, rate-constrained and best-effort traffic can be sent via the same network [SLK+12]. Those types are depicted in Figure 2.4 and explained in the following.

Figure 2.4.: TDMA with time-triggered, rate-constrained and best-effort data streams.

The first traffic type introduced is called Best Effort (BE, colored in green). Whenever a significant event occurs at the sender, the related output message is buffered until the communication system is ready to forward it. The receiver buffers the message in an input queue and consumes it later [Kop08b]. Both buffers can overflow if the network is congested or the sending rate is larger than the receiver's reception rate. These overflows have to be handled using an event-triggered protocol [Kop91]. Without any limitations, it is impossible to provide temporal guarantees. All senders may send messages at the same instant overloading the network. Countermeasures would be buffering, delaying packets at the sender's site or dropping packets. All of them are not suitable for real-time data, wherefore the following to traffic types were developed [Kop11, p. 178].

Rate-Constrained (RC) communication systems (colored in orange) guarantee a maximum bandwidth including a bounded transport latency and jitter. To provide the guarantees, the bandwidth parameters of each application are predefined. In contrast to time-triggered traffic, rate-constrained communication is not deterministic as it does not follow a synchronized time-base [Bel11]. It is possible that some systems exceed their bandwidth as long as other systems are not congested. In this case, the communication system sends the additional messages as best effort. However, the senders are forced to delay their packets if the network cannot handle the increased traffic. In this way, temporal error detection and the protection from babbling idiot can be provided. Typically, there is less traffic compared to the assumed peak [Kop11, p. 180f.].

Finally, Time-Triggered (TT) communication (red-colored streams) is based on an a priori known and periodically repeated communication schedule. Each time-triggered message is sent at a dedicated phase in every period. Using the known schedule, the communication system can assign the required resources to those messages wherefore they are sent in known intervals and without any collisions [Kop08b]. Furthermore, it provides determinism since a sparse time base ensures a consistent temporal order of all messages [Kop07]. The time base can be realized using a synchronized global time which bounds the communication jitter to its precision. Typically, it lies in the sub-microsecond range. An alternative to this approach is using the period of a single leading process. This process establishes a basic period from which all other cycles must be derived [Kop11, p. 184].

### 2.1.6. Real-Time Operating Systems

Operating systems are used to manage the resources of a computer system and to provide a simplified interface for developing applications. It is realized as an additional software layer on top of the bare hardware [TB15, p. 1].

The management of resources covers scheduling, access to memory and input/output devices, protection and synchronization of resources between tasks and interprocess communication. Herein, Real-Time Operating Systems (RTOSs) must take care of a predictable execution [SR04]. This is different from general-purpose operating systems which focus typically on a maximum throughput and fairness [Ler05]. Section 3.4 introduces approaches which try to provide real-time characteristics to standard operating systems. The aim is to exploit comforts from the standard OS like graphical user interfaces, file systems or standard APIs while providing real-time capabilities [Mar18, p. 203f.].

Resources in embedded systems are usually limited. Hence, it should be possible to remove services from the operating systems which are not required. The concept of a micro-kernel provides a configurable operating system according to the hardware resources and needs of the application. Typical elementary functionalities are interprocess communication, synchronization and a few functions for task management. The latter cover creation, activation, blocking and termination of tasks. All remaining functionalities can be implemented in additional modules based on the elementary services. Benefits are an improved usage of limited resources, scalability and portability. Furthermore, the time required to execute system calls is reduced and the micro-kernel is mostly preemptive. This improves timeliness and determinism. As a disadvantage, the short duration of system calls results in many context switches between user and kernel mode. Since less functions are executed in the protected kernel-mode, the protection of resources is decreased further [WB05, p.

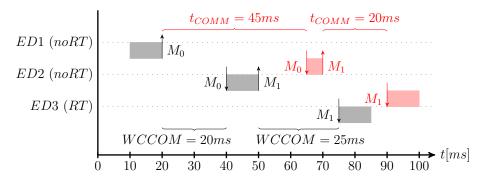

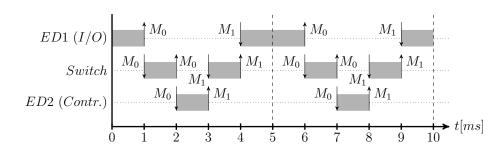

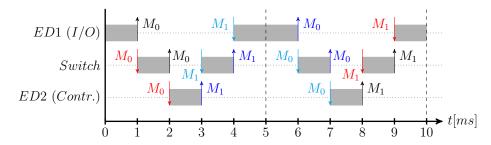

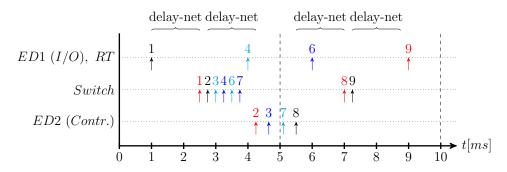

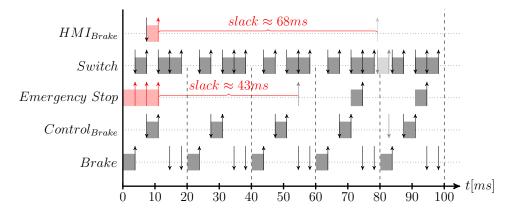

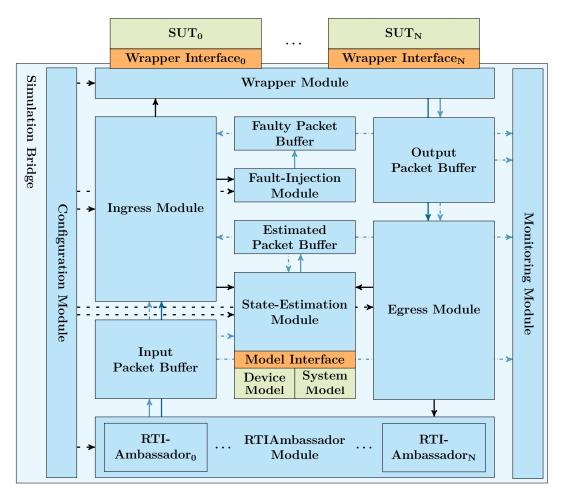

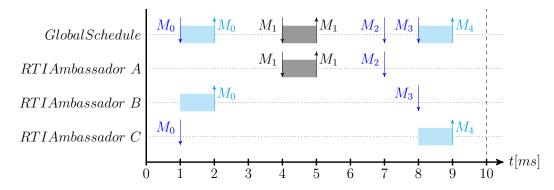

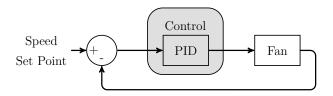

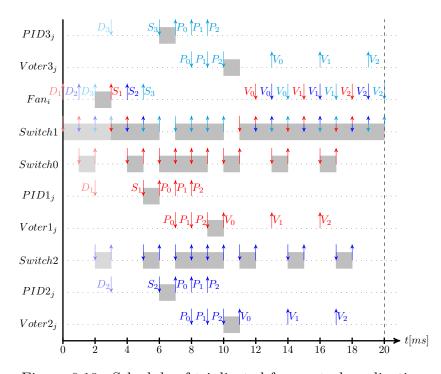

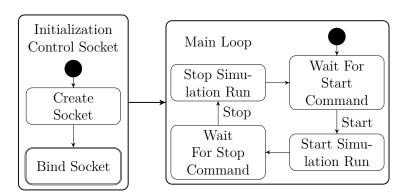

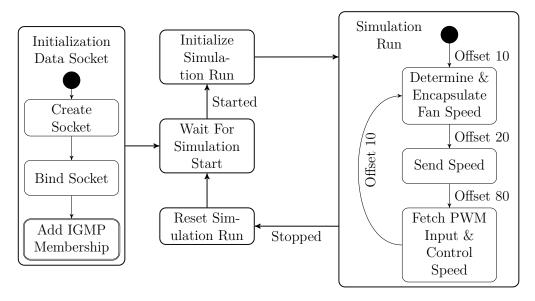

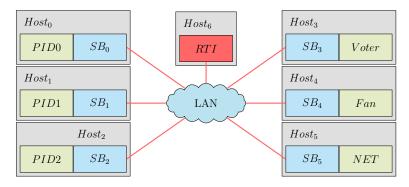

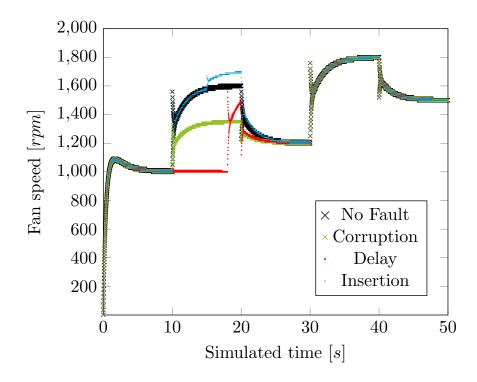

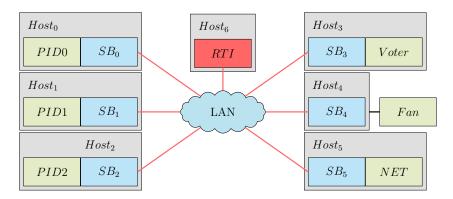

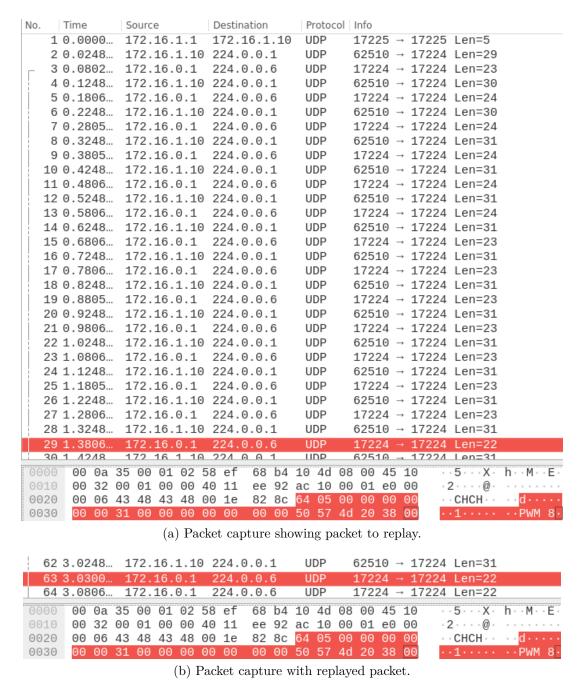

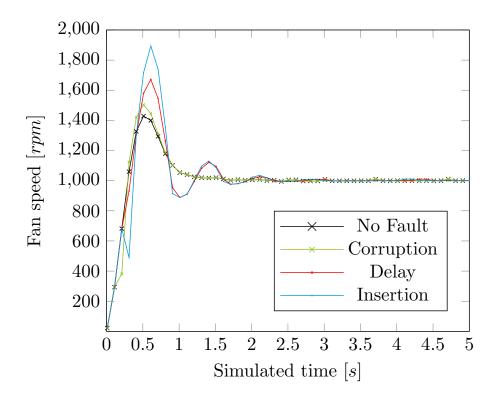

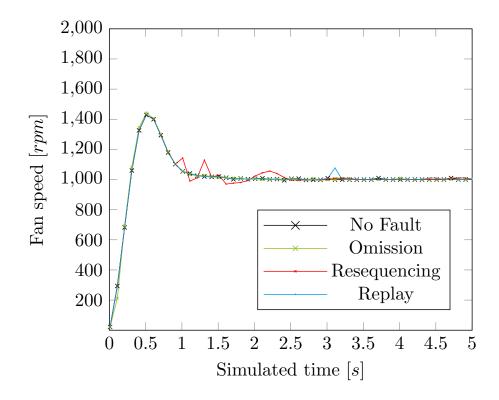

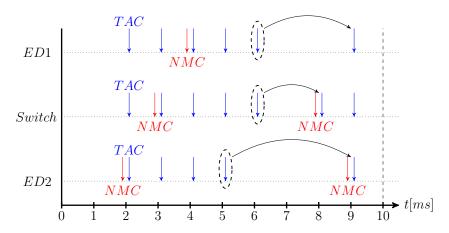

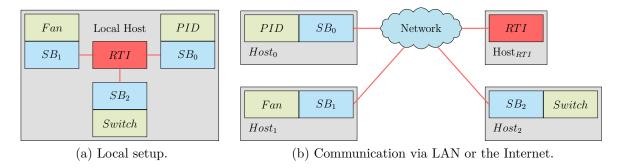

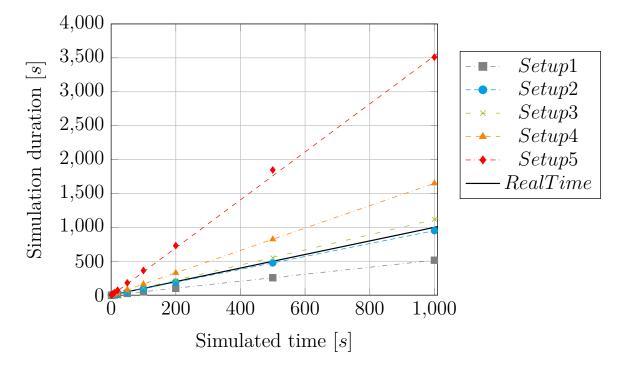

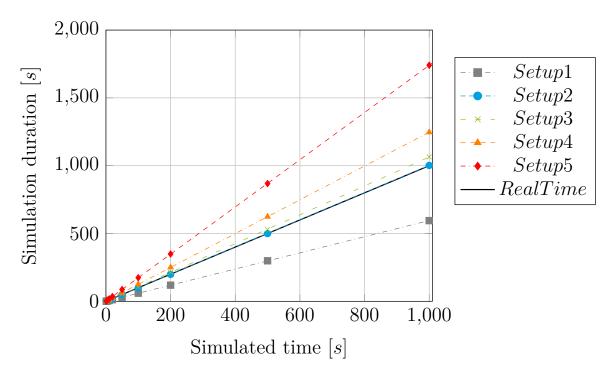

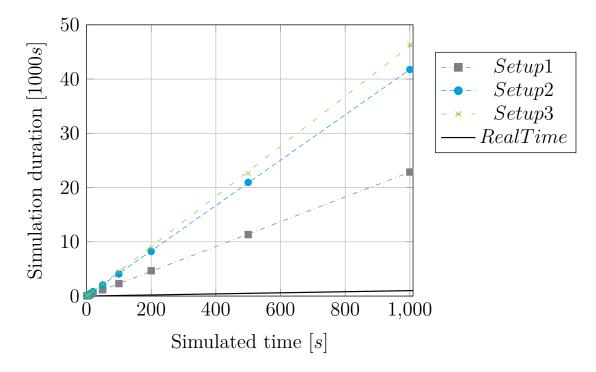

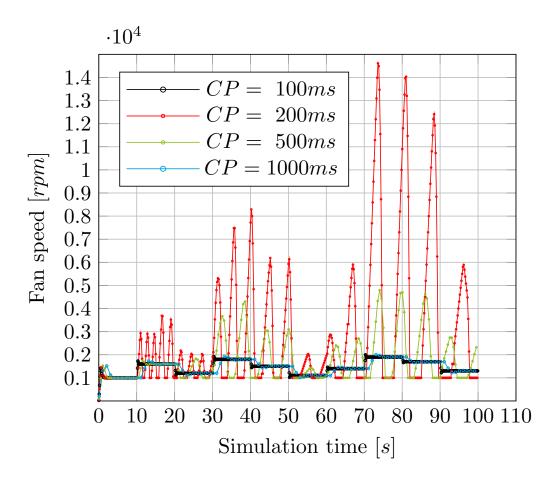

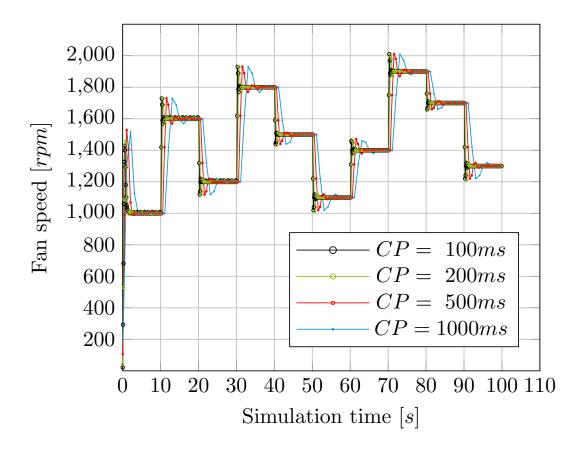

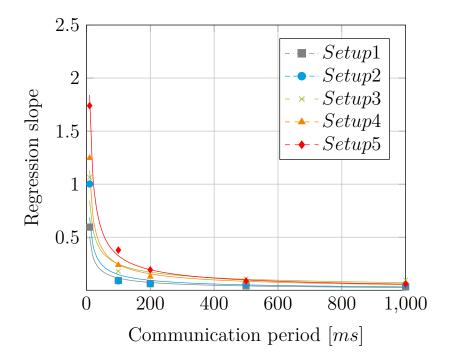

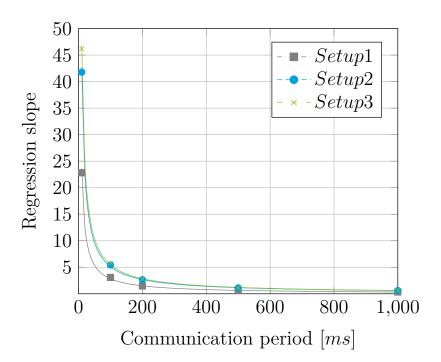

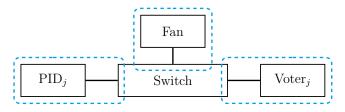

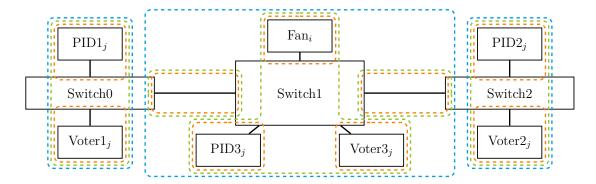

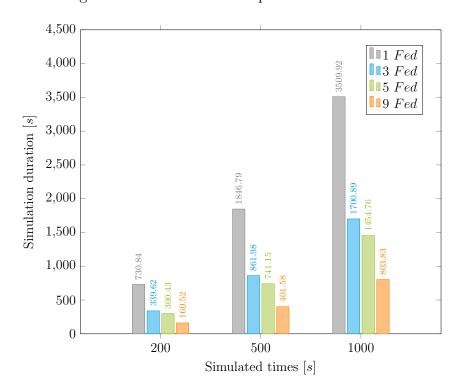

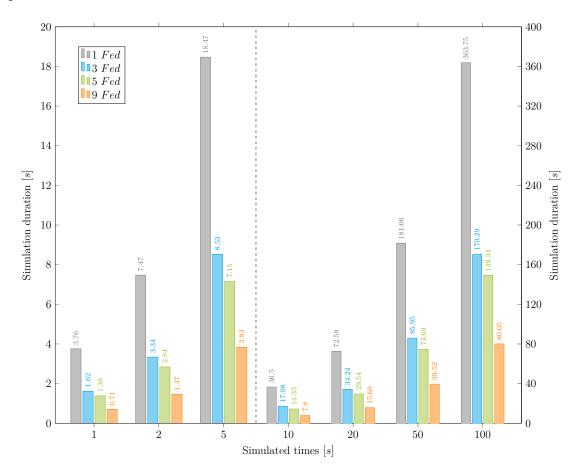

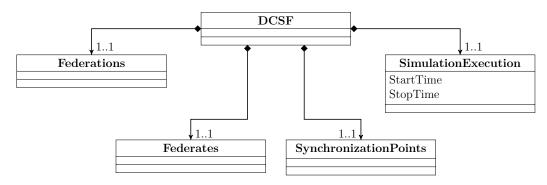

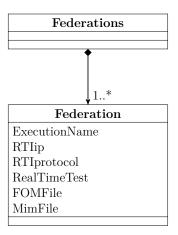

346ff.]. However, some embedded systems are designed for a special purpose and tested to be reliable which is why protection is not always required [Mar18, p. 200].