## Development of a low noise analog readout for a DEPFET pixel detector

DISSERTATION zur Erlangung des Grades eines Doktors der Naturwissenschaften

vorgelegt von Dipl. Phys. Adrian Sorin Niculae

eingereicht beim Fachbereich Physik der Universität Siegen

Siegen 2003

#### Gutachter der Dissertation: Prof. Dr. M. Holder Prof. Dr. P. Buchholz

Datum der Disputation: 23. Januar 2004

Internetpublikation der Universität Siegen: urn:nbn:de:hbz:467-459

To my wife Dana and my children Cristiana and Andrei

### Development of a low noise analog readout for a DEPFET pixel detector

by Adrian Sorin Niculae

Abstract: Silicon pixel detectors have become very popular in a large variety of applications such as experimental particle physics, medical imaging, video and digital cameras. The DEPFET pixel detector is a novel concept of a silicon detector consisting of a JFET transistor integrated on a fully depleted silicon substrate. The signal charge generated by an ionizing particle within the detector substrate is collected at the transistor gate by means of a special depletion scheme called sideward depletion. From the gate, the signal charge modulates directly the JFET channel current. The current signal is further amplified and processed by external electronics. The internal amplification mechanism ensures low noise, even at room temperature. The electrical charge is removed from the JFET gate by a clear mechanism. Two possible clear methods have been suggested: pulsed clear and continuous clear.

In the present work, DEPFET structures with continuous clear mechanism have been studied. A low noise analog readout circuit has been developed in CMOS technology. This readout chip has been tested with different DEPFET pixel structures. By recording energy spectra of known radioactive sources, an electronic noise of about 13 e<sup>-</sup> has been measured at room temperature. The DEPFET device opens therefore new possibilities for applications that require very good energy resolution at room temperature.

# Contents

| <b>1</b> | Introduction                                   |                                                                             |    |  |  |  |  |

|----------|------------------------------------------------|-----------------------------------------------------------------------------|----|--|--|--|--|

|          | 1.1                                            | Interaction of radiation with matter                                        | 2  |  |  |  |  |

|          |                                                | 1.1.1 Interaction of charged particles with matter                          | 3  |  |  |  |  |

|          |                                                | 1.1.2 Interaction of photons with matter                                    | 4  |  |  |  |  |

| <b>2</b> | The DEPFET principle 9                         |                                                                             |    |  |  |  |  |

|          | 2.1                                            | The $p$ - $n$ junction diode                                                | 9  |  |  |  |  |

|          |                                                | 2.1.1 The reverse biased $p^+$ -n junction as a particle detector           | 11 |  |  |  |  |

|          |                                                | 2.1.2 Sideward depletion                                                    | 12 |  |  |  |  |

|          | 2.2                                            | The JFET transistor                                                         | 15 |  |  |  |  |

|          | 2.3                                            | JFET integration in the DEPFET detector                                     | 19 |  |  |  |  |

|          | 2.4                                            | Clear mechanism of the DEPFET detector                                      | 20 |  |  |  |  |

|          |                                                |                                                                             | 22 |  |  |  |  |

|          | 2.5                                            | Description of the investigated DEPFET devices                              | 25 |  |  |  |  |

| 3        | Static measurements of the DEPFET detectors 29 |                                                                             |    |  |  |  |  |

|          | 3.1                                            | Static characteristics of the JFET transistor                               | 29 |  |  |  |  |

|          |                                                | 3.1.1 Static characteristics of the JFET transistor of DEPFET Type-I and II | 29 |  |  |  |  |

|          |                                                | 3.1.2 Static characteristics of the JFET transistor of DEPFET Type-III      | 31 |  |  |  |  |

|          | 3.2                                            | Static characteristics of the clear structures                              | 32 |  |  |  |  |

|          | 3.3                                            |                                                                             | 34 |  |  |  |  |

|          | 3.4                                            | -                                                                           | 35 |  |  |  |  |

| 4        | Sma                                            | all-signal and noise analysis of the DEPFET                                 | 39 |  |  |  |  |

|          | 4.1                                            | Small-signal equivalent circuit of a JFET                                   | 39 |  |  |  |  |

|          | 4.2                                            | Small-signal analysis of the DEPFET device                                  | 40 |  |  |  |  |

|          |                                                | 4.2.1 Source-follower configuration of the DEPFET                           | 40 |  |  |  |  |

|          | 4.3                                            | Noise analysis of the DEPFET                                                | 44 |  |  |  |  |

|          |                                                | 4.3.1 Noise sources in electronic devices                                   | 44 |  |  |  |  |

|          |                                                | 4.3.2 Statistical noise in semiconductor detectors                          | 46 |  |  |  |  |

|          |                                                | 4.3.3 Noise sources in the DEPFET device                                    | 46 |  |  |  |  |

| <b>5</b> | Analog readout in CMOS technology |                                                                                       |     |  |  |  |

|----------|-----------------------------------|---------------------------------------------------------------------------------------|-----|--|--|--|

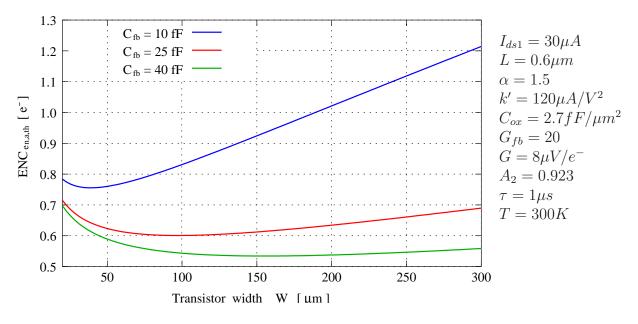

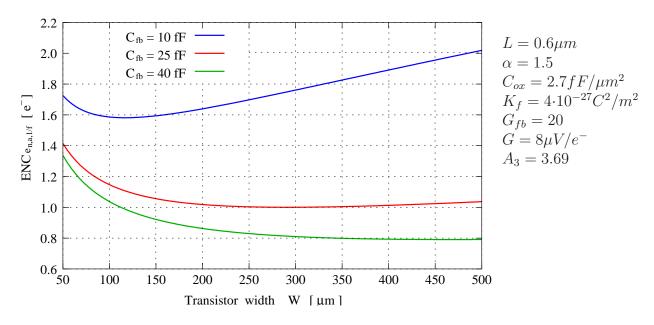

|          | 5.1                               | Noise considerations                                                                  | 56  |  |  |  |

|          |                                   | 5.1.1 Noise optimization of the DEPFET bias current source                            | 56  |  |  |  |

|          |                                   | 5.1.2 Noise optimization of the feedback amplifier                                    | 58  |  |  |  |

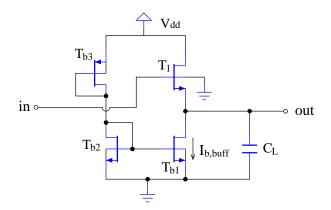

|          | 5.2                               | The voltage feedback amplifier                                                        | 62  |  |  |  |

|          |                                   | 5.2.1 The effect of the finite input and output impedance on the amplifier            |     |  |  |  |

|          |                                   | transfer function                                                                     | 64  |  |  |  |

|          | 5.3                               | Regulated cascode amplifier                                                           |     |  |  |  |

|          |                                   | 5.3.1 Low-frequency analysis of the RGC amplifier                                     | 67  |  |  |  |

|          |                                   | 5.3.2 High-frequency analysis of the RGC amplifier                                    |     |  |  |  |

|          |                                   | 5.3.3 Final design of the core amplifier                                              | 70  |  |  |  |

|          | 5.4                               | The complete design of the feedback amplifier                                         | 73  |  |  |  |

|          | 5.5                               | Shaper design                                                                         |     |  |  |  |

|          |                                   | 5.5.1 Noise considerations                                                            | 76  |  |  |  |

|          |                                   | 5.5.2 CR-RC Shaper                                                                    | 78  |  |  |  |

|          |                                   | 5.5.3 S-G shaper based on differential OTA                                            | 81  |  |  |  |

|          | 5.6                               | Analog output buffer                                                                  |     |  |  |  |

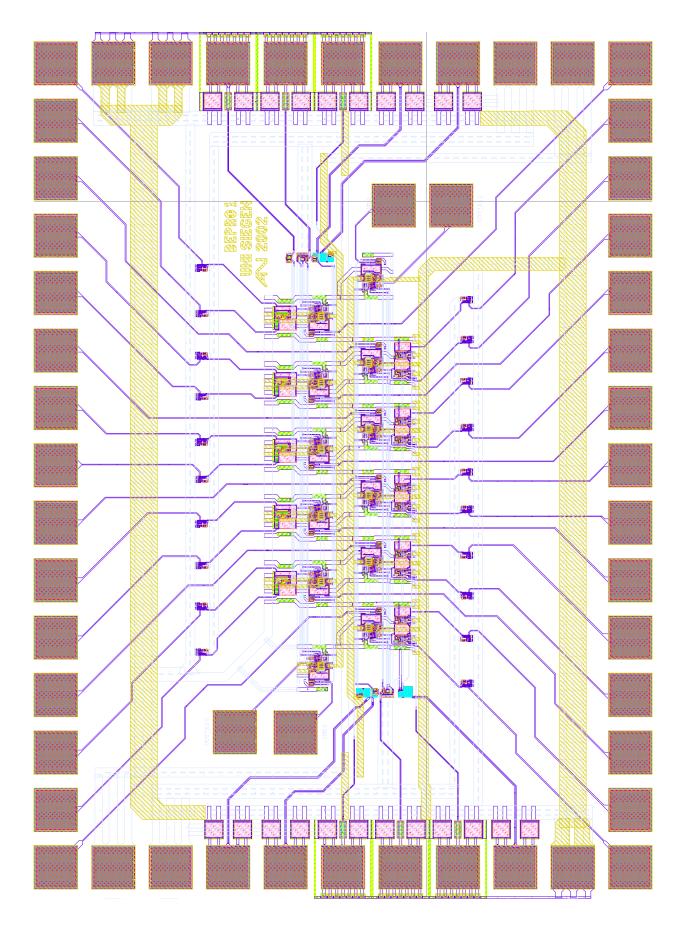

|          | 5.7                               | Multi-channel structure of the readout                                                | 86  |  |  |  |

| 6        | Mea                               | asurement of the readout chip without detector                                        | 89  |  |  |  |

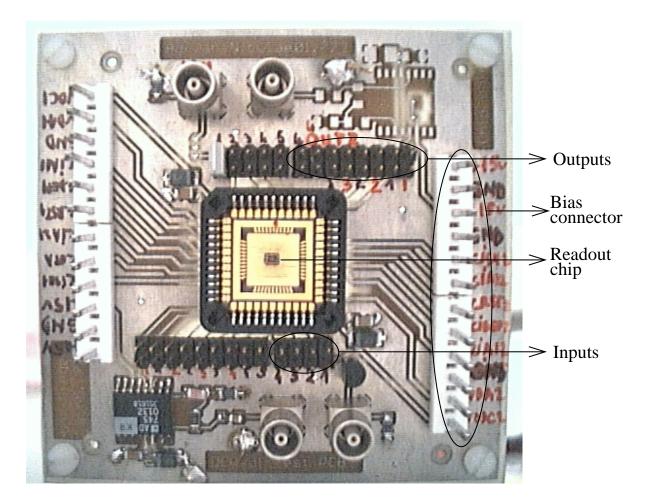

|          | 6.1                               | Setup for testing the readout                                                         | 89  |  |  |  |

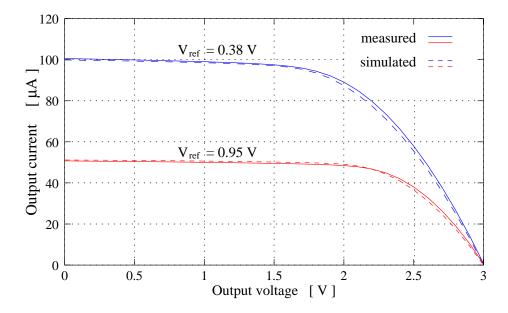

|          | 6.2                               | Measurement of the DEPFET bias current source                                         |     |  |  |  |

|          | 6.3                               | Measurement of the feedback amplifier                                                 |     |  |  |  |

|          | 6.4                               | Measurement of the CRRC shaper                                                        | 93  |  |  |  |

|          | 6.5                               | Measurement of the shaper based on OTAs                                               | 95  |  |  |  |

| 7        | Mea                               | asurements of the readout chip with the detector                                      | 99  |  |  |  |

|          | 7.1                               | Setup for energy measurements                                                         | 100 |  |  |  |

|          |                                   | 7.1.1 Multi-Channel Analyzer (MCA) calibration                                        |     |  |  |  |

|          | 7.2                               | Measurements with DEPFET Type-I and II                                                | 103 |  |  |  |

|          |                                   | 7.2.1 Influence of $V_{dr}$ on the DEPFET performance $\ldots \ldots \ldots \ldots$   | 103 |  |  |  |

|          |                                   | 7.2.2 Influence of $I_{ds}$ on the detector performance $\ldots \ldots \ldots \ldots$ | 105 |  |  |  |

|          |                                   | 7.2.3 Measurement of ENC noise versus shaping time                                    |     |  |  |  |

|          |                                   | 7.2.4 Measurements of the x-ray spectrum of ${}^{55}$ Fe radioactive source           |     |  |  |  |

|          |                                   | 7.2.5 Measurement of the x-ray spectrum of $^{109}$ Cd radioactive source             |     |  |  |  |

|          | 7.3                               | Measurements with DEPFET Type-III and IV                                              | 112 |  |  |  |

| 8        | Sun                               |                                                                                       | 115 |  |  |  |

|          | 8.1                               | Summary and conclusions                                                               |     |  |  |  |

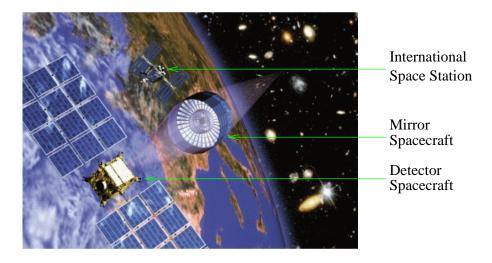

|          | 8.2                               | Possible applications of DEPFET pixel detectors                                       | 116 |  |  |  |

| A        |                                   |                                                                                       | 119 |  |  |  |

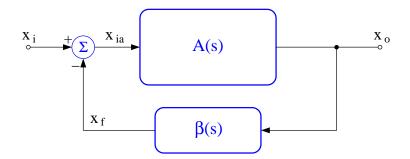

|          | A.1                               | Stability problem in feedback amplifiers                                              |     |  |  |  |

|          |                                   | A.1.1 Frequency analysis: poles and zeros of $A(s)$                                   |     |  |  |  |

|          | A.2                               | High frequency analysis of the RGC amplifier                                          |     |  |  |  |

|          |                                   | A.2.1 Zeros of the transfer function                                                  | 125 |  |  |  |

|               |       | A.2.2 Poles of the transfer function                           |         |         | 125 |

|---------------|-------|----------------------------------------------------------------|---------|---------|-----|

|               |       | A.2.3 Analysis of the voltage transfer function                |         |         | 127 |

|               |       | A.2.4 Stability of the the RGC amplifier: frequency of         | compens | ation . | 129 |

| В             | Cale  | culation of $A_1$ , $A_2$ , $A_3$ for an $n^{th}$ order filter |         |         | 131 |

| $\mathbf{C}$  | Dat   | ta sheets                                                      |         |         | 135 |

|               | C.1   | DEPFET bias current source                                     |         |         | 135 |

|               | C.2   | Feedback amplifier                                             |         |         | 136 |

|               | C.3   | CR-RC shaper                                                   |         |         | 137 |

|               | C.4   | Shaper based on OTAs                                           |         |         | 138 |

|               | C.5   | Output buffers                                                 |         |         | 138 |

| Bi            | bliog | graphy                                                         |         |         | 141 |

| $\mathbf{Li}$ | st of | f Figures                                                      |         |         | 145 |

# Chapter 1 Introduction

The progress in experimental high energy physics (HEP) has pushed the development of more refined techniques in detector physics. Semiconductor detectors have been used for more than twenty years for the detection of ionizing particles. In the meantime the semiconductor detectors have found their application also in consumer electronics (digital cameras, video camcorders based on CCD<sup>1</sup> sensors), in medicine (tomographic systems) or in astrophysics (x-ray and  $\gamma$ -ray cameras)

The most widely spread material for semiconductor detectors is silicon. The reasons for it are that its material structure is very well understood, it generates a natural oxide  $(SiO_2)$  with nearly the same lattice parameters (important for the fabrication of structures such as MOS<sup>2</sup> transistors) and last but not least, the fabrication costs are relatively low.

The simplest semiconductor detector consists of a  $300\mu m$  thick silicon substrate with a diode structure formed on one side. By applying a large reverse voltage, the silicon substrate is depleted of free charge carriers and becomes sensitive to ionizing particles (e.g. high energy charged particles, photons). The signal charges generated by such particles in the detector substrate can be detected as current pulses at the diode node.

To obtain information about the position of the particle hit, the diode structure is fabricated in form of narrow strips (strip detectors) or small rectangular cells (pixel detectors). The input capacity of these detectors is however large and limits the energy resolution of the detector. An improvement in the energy resolution is obtained by employing the principle of sideward depletion [Gat84]. Using this technique, large area detectors can be depleted without having a large capacitance at the input node. The noise performance and therefore the energy resolution is substantially improved, as it is the case of the silicon drift detector (SDD) [Str00, Lec01] or the pn-CCD structure [Str95].

The energy resolution can be further increased by integrating a preamplifier directly on the detector. The detectors in this category are called DEPFET<sup>3</sup> devices [Kem87, Ces96, Kle96] and consist basically of a field effect transistor integrated on a fully depleted substrate. The signal charge is collected underneath the transistor channel and from there, like a transistor internal gate, it controls the channel current. To avoid the overfilling of the internal gate with thermally generated charges, these are cleared out permanently

<sup>&</sup>lt;sup>1</sup>Charge Coupled Device

<sup>&</sup>lt;sup>2</sup>Metal Oxide Semiconductor

<sup>&</sup>lt;sup>3</sup>DEPleted Field Effect Transistor

(continuous clear devices) or at regular time intervals (pulse clear devices). A noise of  $\text{ENC}^4 \approx 5e^-$  at room temperature has been reached with a pulse-clear DEPFET detector [Ulr01].

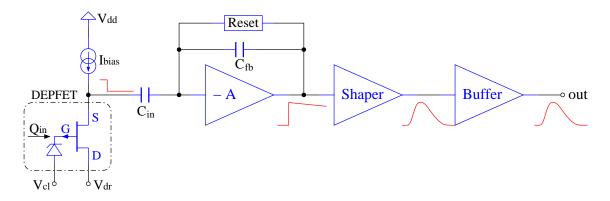

In the present work, the performances of the DEPFET device with continuous clear mechanism are presented. In contrast with the pulse clear DEPFET which, like a CCD structure, is an integrating detector (it collects the charge during a fixed time interval), the continuous clear DEPFET is a detector which is always sensitive and responds individually to each incoming particle. An analog readout for the DEPFET detector has been developed as a dedicated ASIC<sup>5</sup> chip in  $0.6\mu$ m-CMOS (Complementary MOS) technology. The noise performance of the detector-readout system is tested by recording energy spectra from radiative sources of known energy. The DEPFET device can find various applications in High Energy Physics or in the x-ray astronomy, but also in the medicine or in the field of x-ray spectroscopy.

The work is divided in eight chapters. After this short introduction, the interaction of radiation with matter (with emphasis on silicon detectors) is briefly reviewed in this chapter.

The second chapter presents the working principle of the DEPFET detector. The investigated DEPFET structures are also described here. The static measurements of the various DEPFET structures are shown in chapter 3.

Chapter 4 deals with the small-signal and the noise analysis of the DEPFET detector with continuous clear mechanism. The theoretical noise calculations of the DEPFET device are presented here.

The fifth chapter describes the building blocks of the readout circuit. Results of the circuit simulation are also shown in this chapter. The fabricated chip is measured at first without the detector and the results are presented in chapter 6. Chapter 7 shows the noise measurements of the detector-readout system. The noise performances are evaluated from the measured energy spectra of different radioactive sources.

The summary and the conclusion of the results of this work are presented in the last chapter. An outlook towards further improvements and possible application fields is also given here.

#### **1.1** Interaction of radiation with matter

Radiation sees matter in terms of its basic constituents, i.e. an aggregate of electrons and nuclei. The way in which the radiation interacts with these constituents depends on the type of radiation, its energy and the type of material. For charged particles and photons, electromagnetic interaction is the most common process. For neutrons however, strong interaction processes are preferred. In the following discussion, only the interaction of charged particles and photons with matter will be considered.

<sup>&</sup>lt;sup>4</sup>Equivalent Noise Charge

<sup>&</sup>lt;sup>5</sup>Application Specific Integrated Circuit

#### 1.1.1 Interaction of charged particles with matter

When a charged particle passes through matter it interacts with its constituents via the Coulomb force. There are two main processes that characterize the interaction mechanism. On one side, the particle is deflected from its incident direction due to the elastic scattering on nuclei. On the other hand, the particle loses energy mainly due to inelastic collisions with the atomic electrons of the material. For relativistic particles, other processes like the emission of Cherenkov and transition radiation or bremsstrahlung also contributes to the energy loss.

The mean energy loss dE per length dx of a charged particle due to ionization is described by the Bethe-Bloch formula [Gru96]:

$$-\frac{dE}{dx} = 4\pi N_A r_e^2 m_e c^2 \rho z^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ ln \left( \frac{2m_e c^2 \beta^2 \gamma^2}{I} \right) - \beta^2 - \frac{\delta}{2} \right]$$

(1.1)

where

$N_A$  - Avogadro number (6.022 × 10<sup>23</sup> atoms/mol)

- $r_e$  classical electron radius  $(2.817 \times 10^{-13} \text{ cm})$

- $m_e$  electron mass

- c speed of light

z - charge of incident particle in units of elementary charge

- Z, A atomic number and atomic weight of the absorbing material

- $\rho$   $\,$   $\,$  mass density of the absorbing material  $\,$

- *I* mean excitation potential (characteristic of the absorber)

- $\beta$  v/c of the incident particle

$$\gamma$$

-  $(1-\beta^2)^{-1/2}$

$\delta$  - density correction:  $\delta \approx 2ln\gamma + \zeta$ , where  $\zeta$  is a material constant

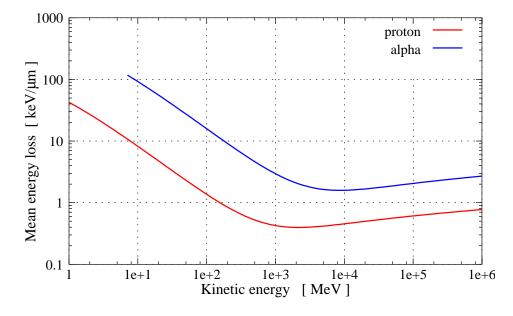

The mean energy loss of an  $\alpha$ -particle and a proton in silicon are plotted in Figure 1.1 as a function of the kinetic energy  $E_k = Mc^2(\gamma - 1)$ . The correction factor  $\delta$  was neglected here.

At low (non-relativistic) energies, the mean energy loss is dominated by the factor  $1/\beta^2$ and decreases with increasing velocity. At  $\beta \approx 0.96$  a minimum energy loss is reached. Particles which correspond to this minimum are called *minimum ionizing particles* (MIP). The minimum energy loss is the same for all the particles with the same charge. The energy deposited by a MIP in a 300  $\mu m$  thick silicon detector is approximately 120 keV.

At high (relativistic) energy the mean energy loss increases with the energy, as the logarithmic term in equation 1.1 becomes large.

Figure 1.1: Rate of energy loss of a proton and an  $\alpha$ -particle in silicon.

#### 1.1.2 Interaction of photons with matter

The interaction of photons (x-ray and  $\gamma$ -rays) with matter is fundamentally different from that of charged particles. In particular, the photon's lack of an electrical charge makes impossible the inelastic collisions with the atomic electrons. Instead, the main interactions of x-rays and  $\gamma$ -rays in matter are: photoelectric effect, Compton scattering and pair production. Depending on the photon energy, one or other of these interaction processes is dominant.

#### Photoelectric effect

The photoelectric effect involves the absorption of a photon by an atomic electron and the subsequent ejection of the electron from the atom. The energy of the outgoing electron is:

$$E_e = E_\gamma - E_b = h\nu - E_b \tag{1.2}$$

where  $E_{\gamma} = h\nu$  is the incident photon energy and  $E_b$  is the electron binding energy. Since free electrons cannot absorb photons for reasons of momentum conservation, the photoelectric effect occurs always on bound electrons, while the recoil momentum is absorbed by the atomic nucleus. The probability of photoelectric absorption on a K-shell electron is particularly large due to the proximity of the nucleus, regarded as the third collision partner.

The ejected electron interacts with the electrons from neighboring atoms and deposits its energy by means of ionization. A hole created in an atomic shell will be occupied by an electron from an outer shell. An amount of energy equal to the difference between the two levels will be released in form of a fluorescence photon or an Auger electron. These are again absorbed by the detector material and almost the entire energy of the incident photon is deposited in the detector. In case that the secondary (fluorescence) photon escapes the detector, an additional line (the so-called *photo-escape* line) occurs in the photon energy spectrum at an energy of approximately  $h\nu - E_K$  ( $E_K$  is the binding energy of the electron in the K-shell). For silicon,  $E_K = 1.84 keV$ .

For photon energies  $E_{\gamma} \gg E_K$ , the cross section for the photoelectric effect is approximately proportional to  $Z^n$  (Z-atomic number) where  $n = [4 \div 5]$ , and inverse proportional to  $E_{\gamma}^{7/2}$  [Leo94]. The higher Z materials are therefore the most favored for the photoelectric absorption of high energy  $\gamma$ -rays.

#### Compton scattering

Compton scattering is one of the best understood processes in photon interactions. The Compton effect describes the elastic scattering of photons on free electrons. The electrons in matter are of course bound. If the photon energy is high with respect to the electron binding energy, the latter can be neglected and the electrons can be considered free.

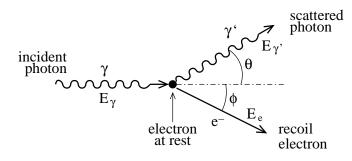

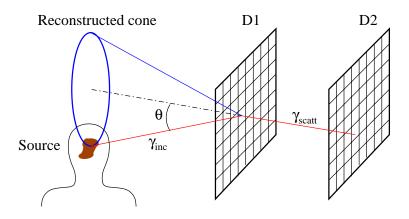

The scattering process is illustrated in Figure 1.2. The incident photon  $\gamma$  with the

Figure 1.2: Compton effect on free electron.

energy  $E_{\gamma}$  hits an electron at rest and is deviated from its initial direction at an angle  $\theta$ . Following the energy and momentum conservation, the electron recoils in a specific direction (angle  $\phi$ ) with the energy  $E_e$ . Applying energy and momentum conservation, the following relations are obtained:

$$E'_{\gamma} = \frac{1}{1 + \varepsilon (1 - \cos\theta)} E_{\gamma}$$

$$E_e = E_{\gamma} - E'_{\gamma}$$

$$\cot\phi = (1 + \varepsilon) \tan\frac{\theta}{2}$$

(1.3)

where  $E'_{\gamma}$  is the energy of the scattered photon and  $\varepsilon = E_{\gamma}/m_ec^2$ . The maximum scattering angle of the electron is  $\phi_{max} = 90^{\circ}$  while the maximum angle for the scattered photon is  $\theta_{max} = 180^{\circ}$ . A maximum energy transfer occurs at this angle and the corresponding electron energy is given by:

(

$$E_e^{max} = \frac{2\varepsilon}{1+2\varepsilon} E_{\gamma} \tag{1.4}$$

$E_e^{max}$  is called the Compton edge.

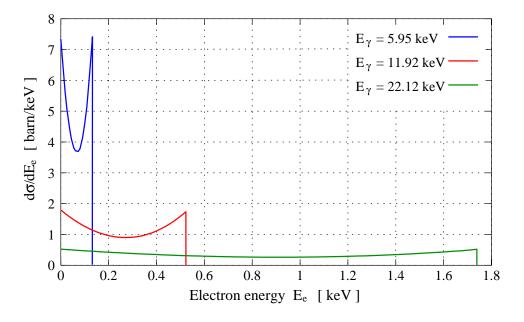

The probability for Compton scattering is typically small, but at energies around 1 MeV, the Compton effect is the dominant process in photon interaction. The energy distribution of the Compton electrons is derived from the Klein-Nishina formula [Kle29]. The differential cross-section of the Compton effect with respect to the electron energy is given by:

$$\frac{d\sigma}{dE_e} = \frac{\pi r_e^2}{m_e c^2 \varepsilon^2} \left[ 2 + \frac{s^2}{\varepsilon^2 (1 - s^2)} + \frac{s}{1 - s} \left( s - \frac{2}{\varepsilon} \right) \right]$$

(1.5)

where  $s = E_e/E_{\gamma}$ . Figure 1.3 shows the energy distribution of the Compton electrons for three different energies of the incident photon.

Figure 1.3: Energy distribution of the Compton electrons for three different energy values of the incident photon.

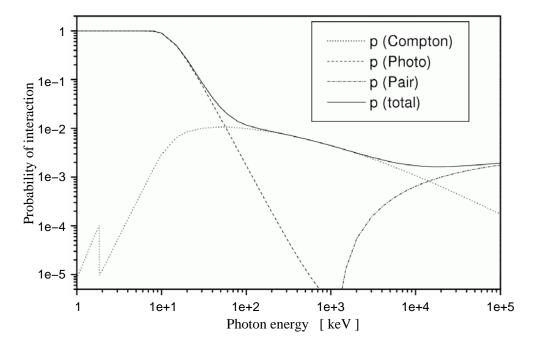

In silicon detectors, the Compton effect becomes dominant over the photoelectric effect at photon energies larger that  $\approx 80 keV$  (see Figure 1.4).

#### Pair production

In the process of pair production, the incident photon is absorbed in the Coulomb field of the nucleus and an electron-positron pair is released. For this reason, the pair production occurs only for photon energies at least twice the rest energy of the electron (511 keV). As a consequence, the pair production process plays a role only for high energetic photons (starting from the MeV range). Figure 1.4 shows the probability of photon interaction in silicon as a function of the photon energy. For energies up to  $\approx 100 keV$  the dominant process is the photoelectric

Figure 1.4: Interaction probability of photons in silicon as a function of energy [Nees00].

effect. The Compton effect plays the dominant role for energies between 100 keV and 10 MeV, where the pair production becomes the significant interaction process.

# Chapter 2 The DEPFET principle

The building principle of the DEPFET detector [Kem87], [Ces96] is described in this chapter. The structure consists basically of two elements: the detector substrate and a JFET transistor integrated directly on the detector (**DEPFET**- <u>DEP</u>leted <u>Field Effect</u> <u>T</u>ransistor). In the following sections each of these elements is described separately. The way in which both elements are integrated in a single structure is also shown here. Furthermore, the structures which are used to clear out the signal charges from the detector are presented in this chapter. The layout of the investigated DEPFET structures is shown at the end of the chapter.

#### 2.1 The p-n junction diode

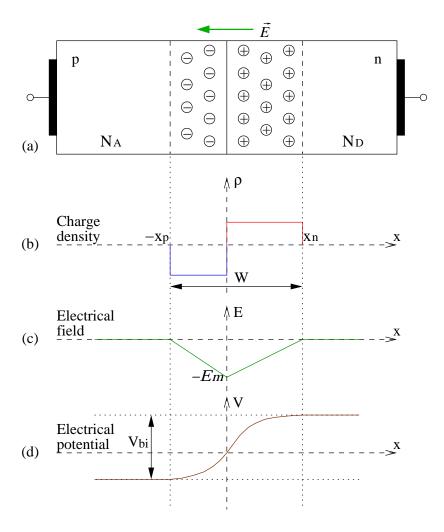

The detection part of the DEPFET detector consists of a p-n junction diode. The properties of such an interface between a p-type and an n-type semiconductor material are used in the most semiconductor detectors. Figure 2.1a shows an idealized p-n junction at equilibrium, i.e. no external voltage is applied on the device.

The junction consists of a p-type (doped with acceptor atoms) semiconductor material brought together with an n-type (doped with donor) semiconductor. The practical realization of a junction is more complex than shown here, special techniques must be used to form such a device [Leo94].

When the two types of semiconductors are brought together, the holes which are major charge carriers in the *p*-type material diffuse into the *n*-type region where they are in minority. The same happens with the electrons (major charge carriers in the *n*-type material) which diffuse into the *p*-type region. The diffusion process leaves back negative ions in the *p*-type semiconductor and positive ions in the *n*-type region. As a consequence, an electrical field gradient is created across the junction (the field is maximum at the interface). This field stops the diffusion process, the system reaches an equilibrium state and a region of immobile space charge is left about the interface (between  $-x_p$  an  $x_n$  in Figure 2.1b). This region is called *depletion zone* or *space-charge region*.

Using Maxwell's equations, the electrical field distribution as well as the electrical potential distribution can be easily calculated [Sze81]. These quantities are plotted in Figure 2.1c and Figure 2.1d. It can be seen that a potential difference occurs across the junction. This potential difference is called *built-in* or *contact* voltage. Denoting the

Figure 2.1: (a) p-n junction at equilibrium; (b) Charge density distribution across the junction; (c)Electrical field distribution across the junction; (d) Electrical potential distribution across the junction.

acceptor and donor impurity concentrations as  $N_A$  and  $N_D$  respectively, the expression of the built-in voltage is given by:

$$V_{bi} = \frac{kT}{q} \ln\left(\frac{N_A N_D}{n_i^2}\right) \tag{2.1}$$

where k is the Boltzmann constant, T is the absolute temperature, q is the electron charge and  $n_i$  is the intrinsic carrier concentration in the semiconductor material.

The width of the depletion zone W is given by:

$$W = \sqrt{\frac{2\epsilon_s}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right)} V_{bi}$$

(2.2)

where  $\epsilon_s$  is the electrical permittivity of the semiconductor material. The extensions of

the depletion zone in the p-region and in the n-region are:

$$x_p = \left(\frac{N_D}{N_A + N_D}\right) W \qquad \qquad x_n = \left(\frac{N_A}{N_A + N_D}\right) W \qquad (2.3)$$

In practice, the impurity concentration in one part of the junction is chosen much higher (several orders of magnitude) than in the other part. The resulting junction is called *one-sided abrupt* junction. Let us assume the case of a  $p^+$ -n junction, i.e.  $N_A \gg N_D$ . The depletion zone extends only into the *n*-region (from equations 2.3:  $x_p \approx 0, x_n \approx W$ ) and equation 2.2 becomes:

$$W = \sqrt{\frac{2\epsilon_s}{q} \frac{1}{N_D} V_{bi}} \tag{2.4}$$

#### 2.1.1 The reverse biased $p^+$ -n junction as a particle detector

Now consider the case of a  $p^+$ -n junction biased with a constant reverse voltage, i.e. the potential at the  $p^+$ -contact is negative with respect to the potential at the n-contact. The applied voltage has the same sign as the built-in voltage and adds to it. As a consequence, the width of the depletion depletion zone increases as equation 2.4 becomes now:

$$W = \sqrt{\frac{2\epsilon_s}{q} \frac{1}{N_D} (V_{bi} + V_r)} \tag{2.5}$$

where  $V_r$  is the magnitude of the applied reverse voltage. If the applied voltage is much larger than the built-in voltage, the later can be neglected and the width of the depletion region becomes proportional to the square-root of the applied voltage.

From equation 2.5 one can obtain the reverse voltage which is needed to deplete entirely a  $p^+$ -n junction detector of thickness d:

$$V_r = d^2 \frac{q N_D}{2\epsilon_s} \tag{2.6}$$

As a numerical example, assume a Si detector of 300  $\mu m$  thickness with the homogeneous doping concentration of the *n*-substrate of  $N_D = 2 \cdot 10^{12} cm^{-3}$ . The reverse voltage which has to be applied in order to fully deplete the detector substrate is then  $V_r \approx 140V$ .

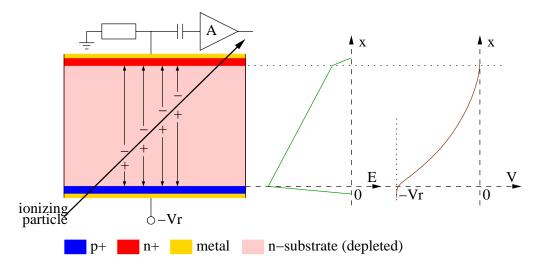

The properties of the depletion zone are particularly attractive for radiation detection. Let us consider the Figure 2.2 where a  $p^+$ -n junction is biased with a reverse voltage  $-V_r$ . The electrical field and potential distribution across the junction are also plotted in the figure. If  $V_r$  is large enough (given by the equation 2.6), the whole detector substrate is depleted and becomes sensitive to ionizing particles. When such a particle crosses the detector, electron-hole pairs are generated within the depleted substrate by means of ionization processes. Due to the electrical field distribution across the structure, the holes drift to the negative contact (the  $p^+$ -side), while the electrons will drift to the positive contact ( $n^+$ -side). Thus, an electrical current proportional to the deposited energy in the detector flows across the device and can be detected with appropriate electronics.

Figure 2.2: Reverse biased  $p^+$ -n junction, electrical field distribution and electrical potential profile across the junction.

#### 2.1.2 Sideward depletion

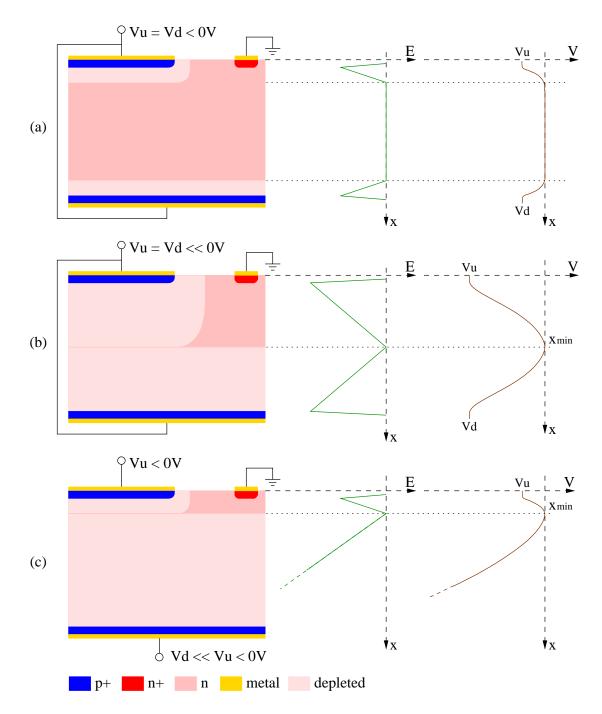

In 1983 Gatti and Rehak [Gat84] proposed a new detector scheme based on sideward depletion. The principle of this scheme is explained in Figure 2.3. The structure shown here consists of two  $p^+$ -n junctions sharing the same n-substrate. The substrate is contacted to ground by means of an  $n^+$ -implantation. If equal reverse voltages  $V_u$  and  $V_d$  are applied to the upper and the lower  $p^+$ -contact respectively, the depletion of the n-substrate starts from both sides (see Figure 2.3a). Increasing the voltage values, the two depletion zones touch each other in the middle of the substrate. The electrical potential seen by electrons has a minimum in this position (see Figure 2.3b). If  $V_u \neq V_d$ , the potential minimum is shifted toward the node with the higher potential. This is the situation depicted in Figure 2.3c.

The electrical potential distribution V(x) can be determined from the one-dimensional Poisson equation:

$$\frac{d^2 V(x)}{dx^2} = -\frac{\rho}{\epsilon_s} \tag{2.7}$$

where  $\rho = q \cdot N_D$  is the charge density in the depleted substrate. Assume that the entire substrate of thickness d is depleted (Figure 2.3b and 2.3c). The solution of the Poisson equation 2.7 with the boundary conditions  $V(0) = V_u < 0$ ,  $V(d) = V_d < 0$  is given by:

$$V(x) = \frac{\rho}{\epsilon_s} x(d-x) + \frac{x}{d} (V_d - V_u) + V_u$$

(2.8)

The position of the potential minimum (the solution of dV/dx = 0) and the potential value at this point are:

$$x_{min} = \frac{d}{2} + \frac{\epsilon_s}{\rho} \cdot \frac{V_d - V_u}{d}; \qquad V(x_{min}) = \frac{V_d + V_u}{2} + \frac{V_o}{4} \left[ 1 + \frac{(V_d - V_u)^2}{V_o^2} \right]$$

(2.9)

Figure 2.3: Principle of the sidewards depletion. Electrical field and potential distribution for various applied voltages.

where  $V_o = d^2 \rho / (2\epsilon_s)$ . Recalling the equation 2.6,  $V_o$  is the voltage necessary to deplete the whole substrate if acting only from one side of the structure (i.e.  $V_u$  or  $V_d$  are set to zero).

For symmetrical boundary conditions  $V_u = V_d$  the position of the potential minimum

is  $x_{min} = d/2$ . Imposing  $V(x_{min}) = 0$ , one obtains from equation 2.9:

$$V_u = V_d = -\frac{V_o}{4} \tag{2.10}$$

The above expression tells us that if the structure is depleted from both sides, the reverse voltage needed for a full depletion of the substrate is a quarter of the value which is needed if depleting from one side only.

For non-symmetrical boundary conditions  $(V_u \neq V_d)$  the position of the potential minimum  $x_{min}$  can be chosen at any point within the detector by choosing the appropriate values of  $V_u$  and  $V_d$ .

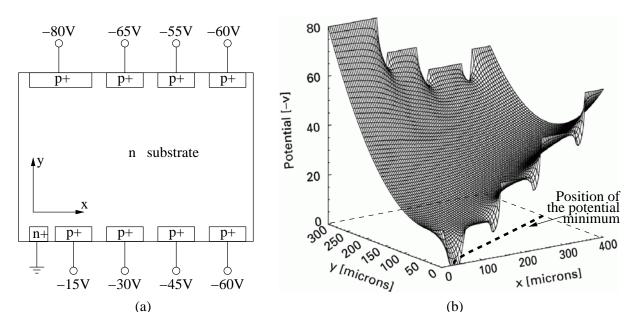

Consider now the structure in Figure 2.4a. The homogeneous  $p^+$ -regions from the lateral sides of the substrate are replaced by a pattern of  $p^+$  implants, each one connected to a separate voltage. Figure 2.4b shows the simulated two-dimensional potential distribution with the given applied voltages. The potential distribution in the *y*-direction has a local minimum whose position varies in the *x*-direction from the center of the substrate to zero with decreasing *x*. The value of this potential minimum also decreases as one

Figure 2.4: (a) Semiconductor drift chamber. (b) Potential distribution inside the detector [Str00].

approaches the  $n^+$ -contact. The signal electrons generated in the detector substrate drift initially to the local potential minima and from there to the  $n^+$ -node (the readout node). This depletion scheme combines the advantages of a large depleted substrate, i.e. large sensitive area, with the small capacitance of the readout node, i.e. large Signal-to-Noise ratio.

The principle that was described above is used in the DEPFET detectors, but also for the silicon drift detectors (SDDs) [Lec01] and for the pn-CCD [Str95, Str00] detectors.

#### 2.2 The JFET transistor

The signal charges from the detector have to be read and amplified by subsequent readout electronics. The first stage of such a readout circuit - the preamplifier - has usually in the input a <u>Field-Effect-Transistor (FET)</u> like MOSFET (<u>Metall-Oxide-Semiconductor-FET</u>) or JFET (<u>Junction-FET</u>).

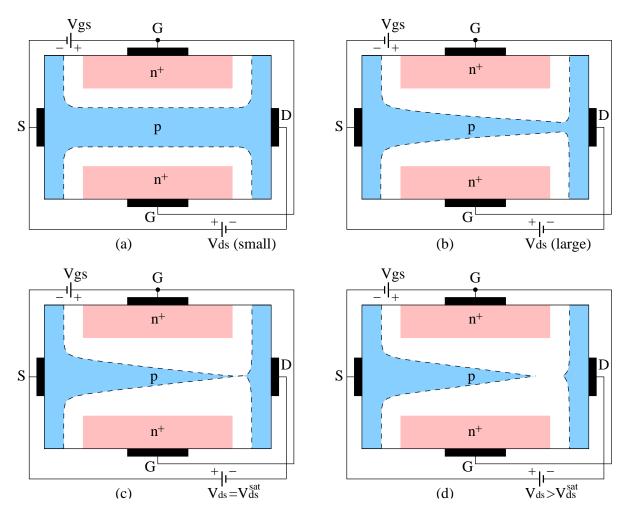

The simplified structure of a *p*-channel JFET transistor is shown in Figure 2.5. The

Figure 2.5: Operation of a p-channel JFET: (a) linear region; (b) non-linear region; (c) pinch-off region; (d) saturation region.

device consists of a *p*-type channel having  $n^+$ -type regions diffused on its lateral sides; these are the so-called transistor gates (G). The contacts at the ends of the transistor channel are called *source* (S) and *drain* (D). Although the device is symmetrical, for a *p*-channel JFET the drain node is negative with respect to the source node. For an *n*-channel device the drain is positive with respect to the source.

If a positive voltage is applied between the gate and the source contact, the gatechannel junctions are reverse biased. Their corresponding depletion zones get wider and the transistor channel becomes narrower. Assume now that a small voltage  $V_{ds}$  is applied between source and drain (Figure 2.5a). The channel is almost of uniform width and the JFET simply operates as a linear resistor with the resistance value controlled by  $V_{gs}$ . The value of the drain-source current  $I_{ds}$  increases linearly with the drain-source voltage.

For larger values of  $V_{gs}$ , a special situation is reached when the entire channel is depleted. No current flows into the channel in this case. The value of  $V_{gs}$  at which this happens is called *pinch-off* voltage, denoted here by  $V_{po}$ .

Now consider the situation illustrated in Figure 2.5b. Here the gate-source voltage is kept constant at a value between 0 and  $V_{po}$  and  $V_{ds}$  increases. As we move along the channel from source to drain, the reverse bias voltage on the gate-channel junction increases and is highest at the drain. The channel acquires a tapered shape and the transistor characteristic  $I_{ds}$ -  $V_{ds}$  becomes non-linear (the channel resistance depends on  $V_{ds}$ ).

Increasing further the value of  $V_{ds}$ , the reverse voltage on the gate-channel junction reaches the pinch-off value  $V_{po}$  at the drain node (see Figure 2.5c). The channel is pinched off at the drain and the channel current saturates. The corresponding drain-source voltage is called *saturation* voltage  $V_{ds}^{sat}$  and is given by  $V_{ds}^{sat} = V_{po} - V_{gs}$ . For values of  $V_{ds}$  larger than  $V_{ds}^{sat}$ , the pinch-off point moves toward the source (Figure 2.5d). The channel current increases slightly with increasing  $V_{ds}$  because of the finite resistance of the depletion region. This is the so-called Early effect.

One distinguishes three regions of operation for the JFET transistor:

- a) Cutoff region:  $V_{gs} \ge V_{po}$  no current flows into the channel

- b) Triode region:  $0 \le V_{gs} \le V_{po}$  and  $V_{ds} \le V_{po} V_{gs}$ ;  $I_{ds}$  is given by [Gray84]:

$$I_{ds} = G_o \left[ V_{ds} - \frac{2}{3} \frac{(V_{gs} + V_{bi} + V_{ds})^{3/2} - (V_{gs} + V_{bi})^{3/2}}{(V_{po} + V_{bi})^{1/2}} \right]$$

(2.11)

c) Saturation region:  $0 \le V_{gs} \le V_{po}$  and  $V_{ds} \ge V_{po} - V_{gs}$ ;  $I_{ds}$  is given by [Gray84]:

$$I_{ds} = I_{ds}^{sat}(1 + \lambda V_{ds}); \qquad I_{ds}^{sat} = G_o \left[ V_{po} - V_{gs} - \frac{2}{3} \frac{(V_{po} + V_{bi})^{3/2} - (V_{gs} + V_{bi})^{3/2}}{(V_{po} + V_{bi})^{1/2}} \right] \quad (2.12)$$

where  $V_{bi}$  is the built-in voltage of the gate-channel junction,  $\lambda$  is the inverse of the Early voltage  $\lambda = 1/V_A$  and  $G_o = aqN_A\mu_hW/L$ , where *a* is the channel depth, *W* is the channel width, *L* is the channel length,  $N_A$  is the impurity concentration in the channel and  $\mu_h$  is the hole mobility.

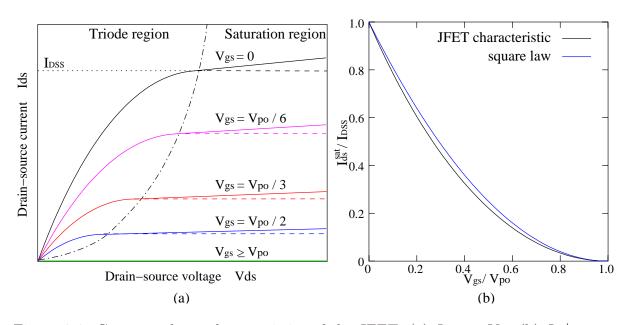

The current-voltage characteristics described by the above equations are plotted in Figure 2.6. The  $I_{ds}$ - $V_{ds}$  characteristic is plotted in Figure 2.6a at different  $V_{gs}$  values. The triode and the saturation regions are separated by the black dash-dotted line. The dashed lines in the saturation region represent the constant saturation current, if the Early effect is neglected.

Figure 2.6b shows the saturation current  $I_{ds}^{sat}$  (given by the equation 2.12) plotted as a function of the gate-source voltage.  $I_{DSS}$  is the  $I_{ds}^{sat}$  value at  $V_{gs} = 0$ . Also plotted in the graph is a square law characteristic given by:

$$I_{ds}^{sat} = I_{DSS} \left( 1 - \frac{V_{gs}}{V_{po}} \right)^2 \tag{2.13}$$

Figure 2.6: Current-voltage characteristics of the JFET: (a)  $I_{ds}$  vs.  $V_{ds}$ ; (b)  $I_{ds}^{sat}$  versus  $V_{gs}$ .

The two curves agree quite well and the equation 2.13 is commonly used as an approximate expression of the transistor saturation current. Combining the equations 2.12 and 2.13, one obtains a simplified characteristic of the transistor in the saturation region:

$$I_{ds} = I_{DSS} \left( 1 - \frac{V_{gs}}{V_{po}} \right)^2 \left( 1 + \lambda V_{ds} \right)$$

(2.14)

The saturation region of the transistor is of most interest in electronics. A small voltage variation on the gate produces a large variation in the saturation current and the transistor behaves like a voltage-controlled current source. The input port of the current source is between gate and source, while the output port is between drain and source. There are two important parameters which characterize the performances of such a device: the *transconductance* and the *output impedance*.

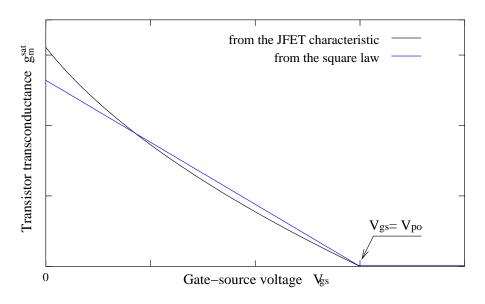

The transconductance parameter denoted by  $g_m^{sat}$  is defined as  $g_m^{sat} = \partial I_{ds} / \partial V_{gs}$ . Using the square law approximation from equation 2.14 and neglecting the Early effect, i.e  $\lambda = 0$ , the JFET transconductance is:

$$g_m^{sat} = -2\frac{I_{DSS}}{V_{po}} \left(1 - \frac{V_{gs}}{V_{po}}\right) = -2\frac{\sqrt{I_{DSS}}}{V_{po}} \sqrt{I_{ds}^{sat}}$$

(2.15)

and is plotted in Figure 2.7. Also plotted here is the transconductance determined from the exact characteristic described by the equation 2.12. The two curves are in good agreement except the region around  $V_{gs} = 0$ .

It can be seen from equation 2.15 that  $g_m^{sat}$  is linear with  $V_{gs}$  and intersects the  $V_{gs}$ -axis at  $V_{po}$ . In practice, this makes possible the accurate determination of the pinch off voltage.

Figure 2.7: Transconductance of the JFET transistor in the saturation region.

The other important parameter - the output impedance  $r_o$  - is defined by  $r_o = \partial V_{ds}/\partial I_{ds}$ . Using the transfer characteristic from equation 2.14, the output impedance is:

$$r_o = \left[ I_{DSS} \left( 1 - \frac{V_{gs}}{V_{po}} \right)^2 \lambda \right]^{-1} \approx \frac{1}{\lambda I_{ds}} = \frac{V_A}{I_{ds}}$$

(2.16)

For large values of  $V_A$  (tens of volt) and values of  $I_{ds}$  of the order of hundreds of  $\mu A$ , the output impedance impedance is very large (hundreds of  $k\Omega$ ). The impact of these two parameters on the JFET performances will be discussed in more details in the next chapter.

The fabrication of a JFET transistor makes use of a special technique called planar technology [Kem84], [Sed98]. Figure 2.8 shows such a JFET device realized in the planar process. The fabrication process begins with an *n*-type silicon substrate which is firstly passivated by thermal oxidation. A  $SiO_2$  layer is thus formed on the top surface. Using photolithographic equipment and special etching techniques, windows are opened in the oxide layer to enable the doping of those regions with the desired doping profiles. The doping process can be performed by means of impurity diffusion and ion implantation. The later is preferred, as it can be performed at low temperature. Additionally, the impurity implantation profiles can be controlled very precisely, by controlling the energy and the dose of the impurity atoms. In order to obtain low ohmic contacts at source and drain,  $p^+$ -regions are formed on the transistor channel. For the external connections, a metal (e.g. Al or Au) layer is evaporated onto the corresponding contact regions.

MOSFET transistors can also be used in the input stage of the detector pre-amplifier. The essential difference is that in a MOSFET the current flows at the semiconductoroxide interface, while in a JFET the current flows within the semiconductor substrate. As the number of the trapping centers is much larger at the semiconductor surface, the MOSFET has a considerably larger "1/f" noise than the JFET transistor. In high energy

Figure 2.8: Realization of a JFET with the planar technology.

application, the semiconductor-oxide interface of the MOSFET can be easily damaged by ionizing particles, in contrast to the JFET transistor which has a better radiation hardness.

#### 2.3 JFET integration in the DEPFET detector

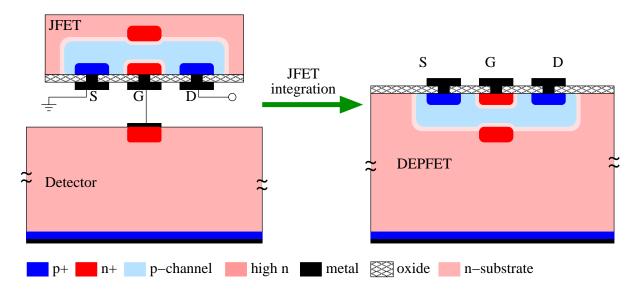

The charge signals from a semiconductor detector have to be further amplified and processed by a readout system. The basic idea in realizing a DEPFET detector is to integrate the first component (usually a JFET or a MOSFET transistor) of such a circuit directly on the detector substrate. The integration scheme is explained in Figure 2.9 The readout

Figure 2.9: The JFET transistor integration in the DEPFET detector.

node of the detector merges with the internal gate of a *p*-channel JFET transistor, as they have the same type of impurity implantation. Combining these two structures with the principle of sideward depletion, one obtains the DEPFET detector which is an active detector, i.e. detector with integrated pre-amplifier.

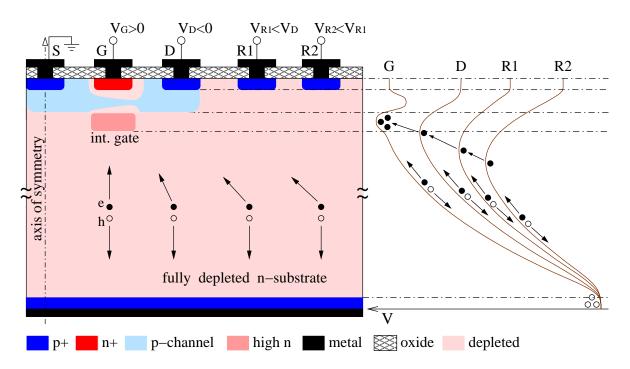

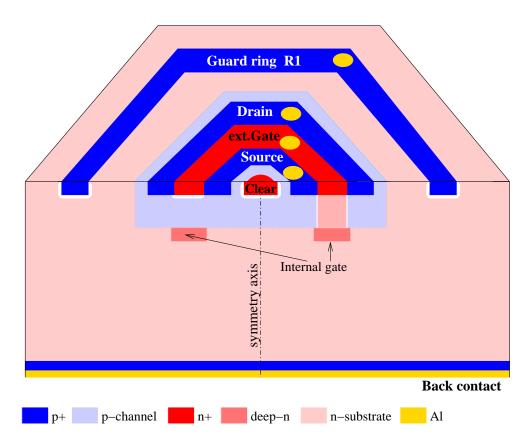

The structure of a depleted DEPFET detector is shown schematically in Figure 2.10. The device has a cylindrical symmetry with respect to the vertical axis at the JFET source. The additional  $p^+$ -type guard rings  $(R_1, R_2)$  formed around the JFET channel are used to shape the electrical potential in the detector substrate. A potential minimum for electrons is created underneath the transistor channel (recall the sideward depletion scheme explained in the section 3.1). This potential minimum is locally confined to the internal gate region, due to the its higher *n*-concentration.

Figure 2.10: The working principle of the DEPFET detector; electrical potential distribution across the detector.

An ionizing particle which hits the detector produces electron-hole pairs in the depleted substrate. The holes drift to the most negative node (the  $p^+$ -contact on the back side), while the electrons drift to the potential minimum formed at the internal gate. They induce a negative voltage change on the small equivalent capacitance of the internal gate and the transistor current increases. This current change is proportional to the number of electrons in the internal gate and is further amplified and processed by an appropriate readout circuit.

#### 2.4 Clear mechanism of the DEPFET detector

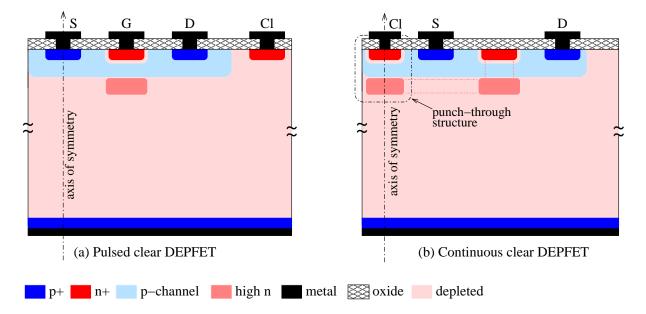

The internal gate of the DEPFET collects not only the signal electrons generated by ionizing particles, but also the electrons that are thermically generated in the depleted substrate. To prevent the over-filling with electrons at the potential minimum and therefore the detector becoming insensitive, a "clear" mechanism has to be employed. There are two methods of removing the collected charges from the DEPFET internal gate: pulsed clear mechanism and continuous clear mechanism.

Figure 2.11: The clear mechanism of the DEPFET detector: (a) pulsed clear DEPFET and (b) continuous clear DEPFET.

In the case of the pulsed clear DEPFET (see Figure 2.11a), an  $n^+$ -region is implanted on the detector, outside the guard ring structure (not shown here). A positive voltage pulse is applied periodically to the clear contact (Cl) and the electrons from the internal gate drift to the contact within the time duration of the applied pulse. The dead time introduced by applying the clear pulse is much shorter than the detector sensitive time. In normal operation, electrons are collected at the internal gate irrespective of whether the transistor is switched on or off. The collected signal charge is nevertheless detected when the JFET is switched on (at regular time intervals). The pulsed clear DEPFET is thus an integrating detector device.

In the case of the continuous clear DEPFET (Figure 2.11b) an  $n^+$ -implant region is formed on the transistor channel near the source. This region forms together with the *p*-region of the transistor channel and the high *n* implant of the internal gate a so-called *punch-through* structure. The properties of the structure are discussed in details in the next sub-section. When a constant positive voltage is applied to the clear contact, a small steady current flows through the structure and removes continuously the electrons collected at the internal gate.

In the devices which were used in the present thesis, the transistor gates are connected by a vertical opening in the channel implantation. This leads to an increased transconductance, as the transistor current is controlled from both sides of the channel. Furthermore, since the internal gate voltage can be controlled by the clear voltage (more about this in the following sub-section), the upper gate needs no external connection; its length can be reduced to the photolithographic limit, thus reducing the gate capacitance and increasing the signal-to-noise ration.

In contrast to the pulsed clear DEPFET, the continuous clear DEPFET is a counting detector. This means that the detector is continuously sensitive and responds to any charge pulse generated in the detector substrate. In a pixel matrix configuration, all the DEPFET cells have to be read individually. This can be done by employing a special connection technology called *bump bonding*. Each pixel in the detector matrix is connected to the corresponding pixel in the readout electronics matrix through a metal bump. A continuous clear DEPFET matrix is thus appropriate for applications with low counting rates.

#### 2.4.1 The $n^+$ -*p*-*n* punch-through clear structure

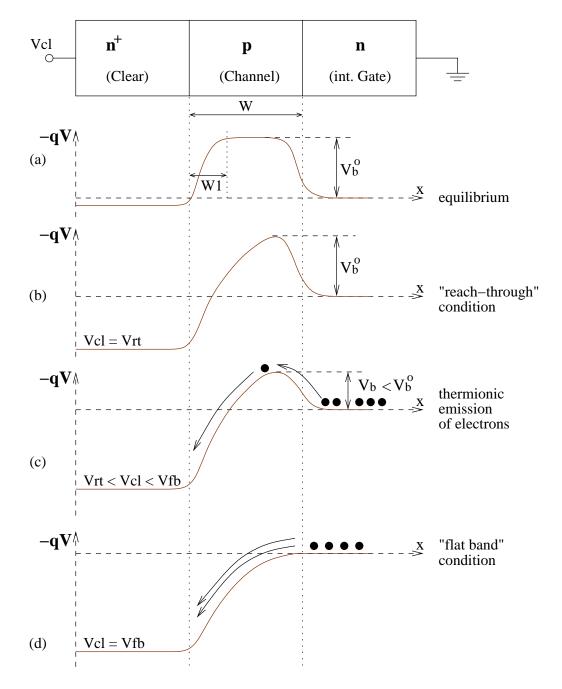

The working principle of the punch-through structure [Sze81] is described in Figure 2.12 The structure consists of two semiconductor junctions  $n^+$ -p and p-n, sharing the same p-region of width W. To illustrate in a simple way how the structure works, it is assumed that the n-region is connected to ground (this is not the case in the real operation of the DEPFET detector).

The potential distribution at equilibrium is shown in Figure 2.12a. The electrons from the *n*-region see a potential barrier of height  $V_b^o$  and cannot enter the *p*-region. When a positive voltage  $V_{cl}$  is applied, the  $n^+$ -*p* junction is reverse biased. The current which flows through the structure is practically the leakage current of the reverse bias junction. This current is mainly due to the generation-recombination processes in the depletion zone and is proportional to the depletion width  $W_1$  [Sze81]:

$$J_{g-r} = \frac{q \cdot n_i}{\tau_e} W_1 \propto \sqrt{V_{cl} + V_b^o} \tag{2.17}$$

where  $n_i$  is the intrinsic carrier concentration and  $\tau_e$  is the effective lifetime.

Increasing the value of  $V_{cl}$ , the depletion zone of the  $p^+$ -n junction widens. At a voltage value called *reach-through* voltage  $V_{rt}$ , the depletion regions of both junctions touch each other (see Figure 2.12b). If  $V_{cl}$  is increased beyond the reach-through value (Figure 2.12c), the potential barrier  $V_b$  decreases and the p-n junction becomes forward biased. Electrons from the n-region injected into the p-region by means of thermionic emission, drift very fast to the  $n^+$ -region due to the electrical field distribution. The current increases exponentially with the applied voltage and is given by [Chu72]:

$$J_{n \to p} = A^* \cdot T^2 exp \left[ -\frac{q(V_{fb} - V_{cl})^2}{4kT \cdot V_{fb}} \right]$$

(2.18)

where  $A^*$  is the Richardson constant for electrons and T is the absolute temperature. The voltage  $V_{fb}$  is called *flat-band* voltage and is the value of the applied voltage at which the potential barrier  $V_b$  vanishes completely (Figure 2.12d). The expression of  $V_{fb}$  is given by (see equation 2.6):

$$V_{fb} = \frac{qN_A}{2\epsilon_s}W^2 \tag{2.19}$$

Figure 2.12: The punch-through structure. Potential distribution across the structure at (a) equilibrium, (b) reach-through condition, (c) thermionic emission of electrons and (d) flat-band condition.

where W is the width of the p-region and  $N_A$  is the impurity concentration in the p-region.

If the injected current is sufficiently high such that the injected carrier density is comparable to the ionized-impurity density  $N_A$ , the mobile charge carriers influence the field distribution in the drift region. This is the so-called *space-charge-limit* effect. The current density saturates to its asymptotical limit given by [Chu72]:

$$J_s = q N_A v_s \frac{V}{V_{fb}} \tag{2.20}$$

where  $v_s$  is the scattering-limited velocity.

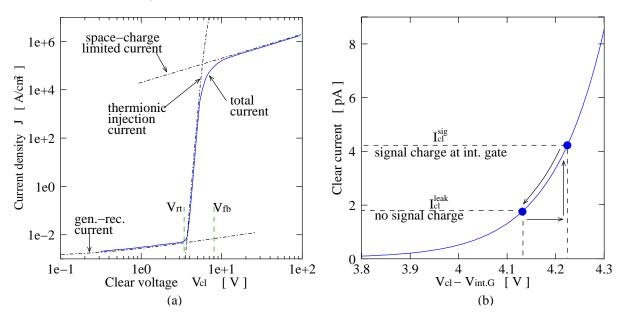

The current-voltage characteristic described by the equations 2.17, 2.18 and 2.20 are plotted in Figure 2.13a. One can see the three operation regions that were discussed above: the generation-recombination current at  $V_{cl} < V_{rt}$ , the exponential increase of the thermionic emission current for  $V_{cl} > V_{rt}$  and the space-charge-limit effect at large values of the current density.

Figure 2.13: (a) Current-voltage characteristic of the punch-through structure; (b) same as (a) but in linear scale.

Figure 2.13b explains the operation of the punch-through structure when used for the DEPFET clear mechanism. The voltage on the x-axis is the now difference between the clear potential and the internal gate potential, as the high *n*-region of the DEPFET internal gate is not connected to ground. The DEPFET substrate is depleted and the current that flows through the structure is the leakage current of the depleted substrate  $I_{cl}^{leak}$ . Since this current is very low (order of pA), only a narrow region (around the reachthrough point) of the current-voltage curve in Figure 2.13a will characterize the DEPFET clear mechanism.

Assume first that no signal charge is generated in the detector substrate. The constant leakage current  $I_{cl}^{leak}$  removes the electrons that are thermically generated in the depleted substrate. The potential difference between clear and internal gate will adjust itself to a value given by the current-voltage characteristic in Figure 2.13b. A change in the clear voltage is then automatically followed by the same change in the internal gate voltage. This is the way in which the gate potential of the JFET transistor can be controlled via the clear contact.

If an ionizing particle hits the detector, the generated signal electrons are collected at the internal gate. The gate potential becomes more negative, and correspondingly, the clear current increases on the I - V characteristic to the value  $I_{cl}^{sig}$ . This current starts to empty the internal gate at a higher rate (proportional to the signal current). As the electrons progressively leave the internal gate, its potential returns slowly to the initial value and the clear current decreases towards  $I_{cl}^{leak}$ . The device has returned now to its operation point.

#### 2.5 Description of the investigated DEPFET devices

The continuous clear DEPFET devices that are investigated within this work were fabricated at the Semiconductor Laboratory of Max Plank Institute in Garching [SEM03]. The structures are fabricated in planar technology [Kem84] on a high resistance silicon *n*-substrate. We investigate here four different versions of DEPFET detectors which are realized as single pixel structures on a silicon substrate. They are denoted by Type-I, -II, -III and -IV.

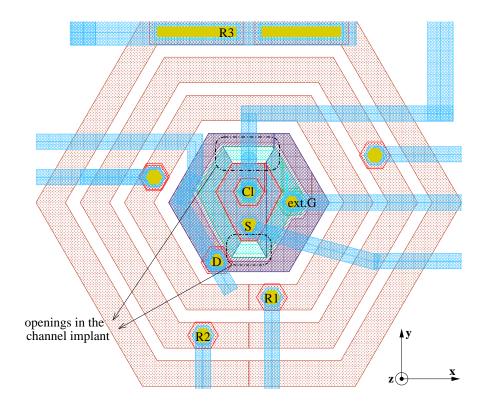

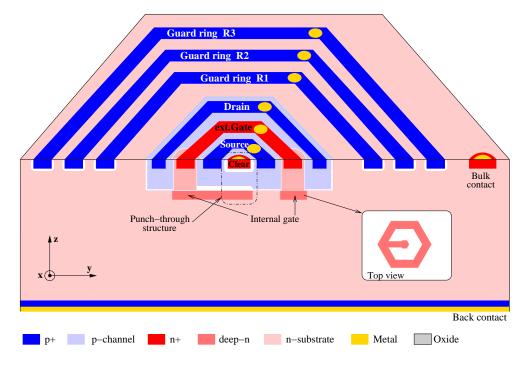

The layout of the Type-I DEPFET is shown in Figure 2.14. The structure consists of three guard rings of hexagonal shape formed around a *p*-channel JFET transistor also of hexagonal shape. The clear contact is in the center of the structure. The two openings in the channel implantation region connects the transistor gates. In order to be able to measure the transistor characteristics independently on the clear structure, the external gate is also contacted. A three-dimensional schematic view with a transverse cut through the device is shown in Figure 2.15. One can see here also the shape of the internal gate region (*deep-n* implantation) and the  $n^+$ -p-n punch-through structure under the clear contact.

Figure 2.14: Layout of the continuous clear DEPFET of Type-I [SEM03].

Figure 2.15: A transverse cut through the DEPFET detector of Type-I.

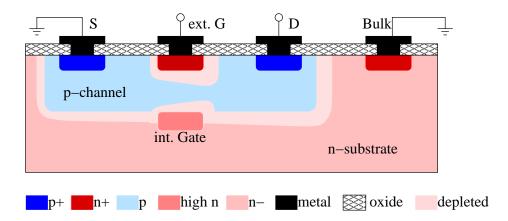

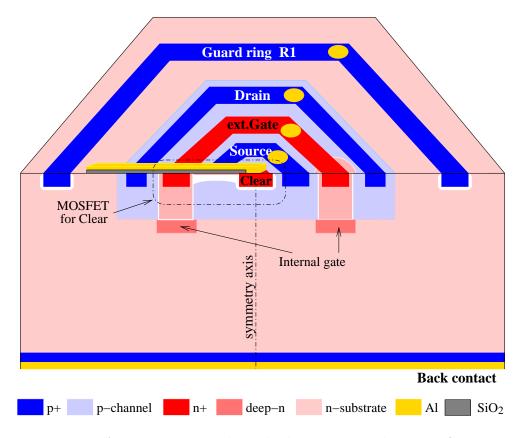

The DEPFET structure of Type-II is identical to the one of Type-I, except for the clear mechanism. Although it is still a continuous clear mechanism, it does not employ a punchthrough structure, but an *n*-channel MOSFET structure operated in the subthreshold region. Figure 2.16 shows a transverse cut through the DEPFET structure. For simplicity, only one guard ring is drawn here. The n-MOSFET structure which is used for the clear mechanism consists of the  $n^+$  clear implant (the MOSFET drain), the external gate  $n^+$ implant (the MOSFET source) and the *p* implant of the JFET channel as the MOSFET substrate (the  $p^+$  implantation of the JFET source is missing in the region underneath the MOSFET). The metal layer which connects the clear contact is also used for the gate of the MOSFET. The structure works therefore as transistor in the diode configuration.

Figure 2.16: A transverse cut through the DEPFET detector of Type-I.

Like in the case of the punch-through structure, the clear current flowing through the MOSFET structure is the detector leakage current. At these current values, the current-voltage characteristic is exponential [Alle02] (the MOSFET is in the sub-threshold region). The internal gate voltage can be controlled via the clear voltage in the same way as for the DEPFET detector with the punch-through structure for clear.

The DEPFET of Type-III and -IV have the same clear mechanism as Type-I and -II, respectively, but the JFET is slightly different. To reduce the dimensions of the JFET transistor and therefore the internal gate capacity, the source, gate and drain implants are adjacent to each other. Figure 2.17 shows a similar cut through the DEPFET devices of last two types, the clear structure missing in the drawing.

Figure 2.17: A transverse cut through the DEPFET detector of Type-III and IV.

Since no channel region is left between source and gate or between gate and drain, the JFET channel current flows deep in the channel and therefore, avoids the trapping centers which are present at the surface. The "1/f" noise component can be reduced in this way [Lut99].

## Chapter 3

# Static measurements of the DEPFET detectors

This chapter presents the static characteristics measured for the four types of DEPFET structures. The measurements include the transistor characteristics, the characteristics of the clear structure, the depletion characteristics of the detector substrate and again the characteristics of the JFET, but measured with the detector substrate depleted.

#### 3.1 Static characteristics of the JFET transistor

The static characteristics of the JFET transistor are measured at first independently on the detector substrate. The JFET source is connected to ground, external voltages are applied to the external gate and drain contacts and all the other DEPFET nodes (back contact, substrate, guard rings and clear contacts) are left unconnected.

#### 3.1.1 Static characteristics of the JFET transistor of DEPFET Type-I and II

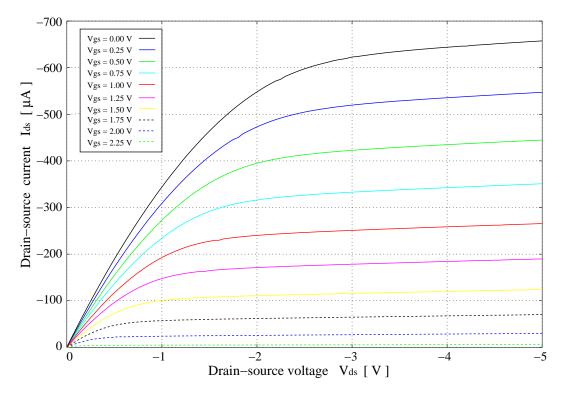

The  $I_{ds}$ - $V_{ds}$  characteristics of the JFET transistor from the first two types of DEPFET are plotted in Figure 3.1. The drain-source current  $I_{ds}$  is measured as a function of the drain-source voltage  $V_{ds}$  for different values of the gate-source voltage  $V_{gs}$ . One can see the linear increase of the current at small values of  $V_{ds}$  and the saturation region for larger values of  $V_{ds}$  (compare to Figure 2.6 in chapter 2).

Figure 3.1:  $I_{ds}$ - $V_{ds}$  characteristic of the JFET (DEPFET of Type-I and II).

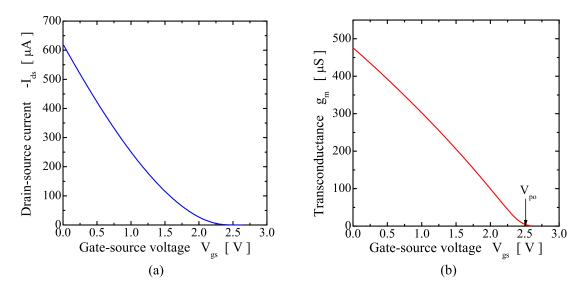

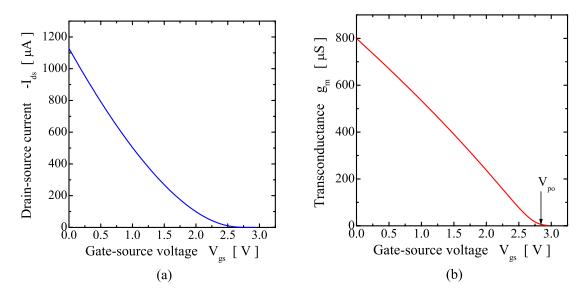

With the drain-source voltage set to  $V_{ds} = -3V$  (JFET in saturation), the drainsource current is measured with respect to the gate-source voltage. The characteristic is plotted in Figure 3.2a. The JFET transconductance parameter  $g_m$  which is proportional

Figure 3.2: (a)  $I_{ds}$ - $V_{gs}$  characteristic; (b) JFET transconductance  $g_m$ .

to  $\sqrt{I_{ds}}$  (see the last part of equation 2.15) is plotted in Figure 3.2b. It can be seen that  $g_m$  varies almost linearly with  $V_{gs}$  and the value of the pinch-off voltage  $V_{po}$  (at which  $g_m$  intersects the  $V_{qs}$ -axis) is about 2.5 V.

## 3.1.2 Static characteristics of the JFET transistor of DEPFET Type-III and IV

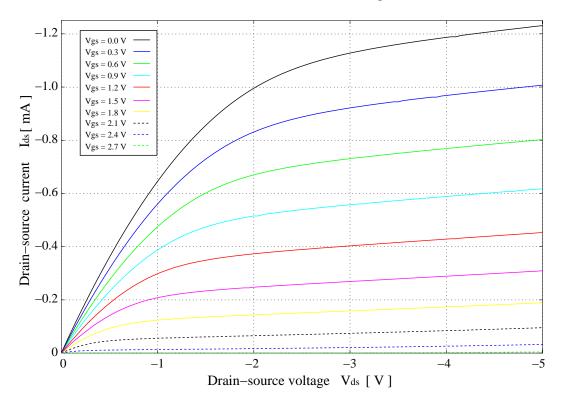

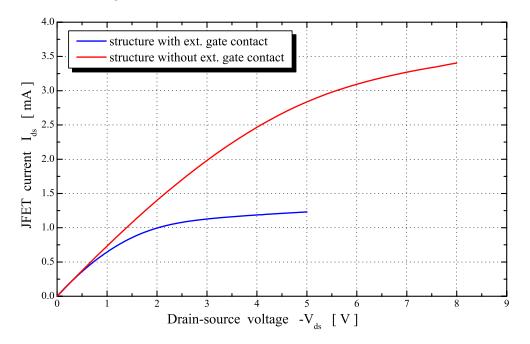

The  $I_{ds}$ - $V_{ds}$  characteristic of the JFET transistor from the DEPFET Type-III and IV are plotted in Figure 3.3. Notice that at similar values of  $V_{qs}$ , the drain source current is

Figure 3.3:  $I_{ds}$ - $V_{ds}$  characteristic of the JFET (DEPFET of Type-III and IV).

larger than in the JFET of the previous type. The design length of the JFET gate is the same for both transistors, but differences occur after the fabrication process. While in the previous JFET type, the effective gate length is larger than the design value due to the lateral diffusion, the effective gate length of the JFET of this type is smaller due to the vicinity of the  $p^+$ -implant regions of source and drain. Consequently, the parameter  $G_o$  from equation 2.12 is larger ( $G_o$  is inverse proportional to the channel length) and the drain-source current is larger.

The  $I_{ds}$ - $V_{gs}$  characteristic (measured at  $V_{ds} = -3V$ ) and the transistor transconductance are plotted in Figure 3.4. The pinch-off voltage is  $V_{po} \approx 2.8V$ .

Figure 3.4: (a)  $I_{ds}$ - $V_{gs}$  characteristic; (b) JFET transconductance  $g_m$ .

## **3.2** Static characteristics of the clear structures

The static characteristics of the two types of clear structures are measured also independently on the DEPFET substrate. Recall that the internal gate is connected to the external gate through the openings in the channel implant; the potential of the internal gate is set to ground by setting the external gate to ground. With all the other nodes left unconnected, an external voltage is applied to the clear contact and the clear current is measured.

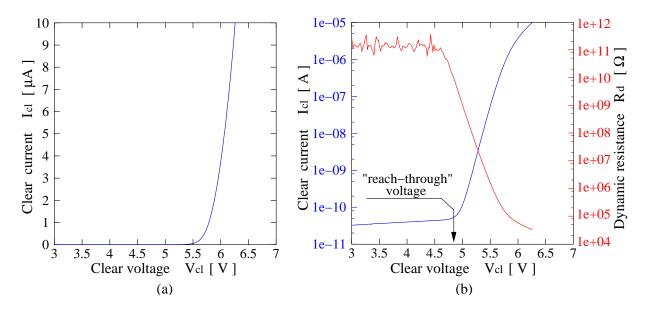

Figure 3.5a shows the measured characteristic of the punch-through clear structure used in the DEPFET device of Type-I and III. The same curve is plotted at semilogarithmic scale in Figure 3.5b. The reach-through voltage  $V_{rt}$  is about 4.8V and the current increases exponentially with the voltage for  $V_{cl} \geq V_{rt}$ . The space-charge-limited region where the current starts to saturate becomes visible at high current values. The dynamic resistance determined from the  $I_{cl}-V_{cl}$  curve as  $R_d = dV_{cl}/dI_{cl}$  is plotted in the same graph (red curve). This resistance together with the internal gate equivalent capacitance defines the time constant of the clear mechanism. One can see that at small values of the clear current, the equivalent resistance has values in the range of hundreds of  $G\Omega$ . With the internal gate capacitance in the range of tens of fF, a clear time constant of the order of ms is achieved.

Figure 3.5: Static characteristic of the punch-through clear structure.

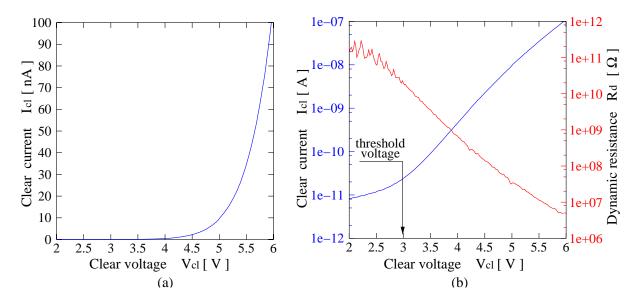

The static characteristics of the MOSFET clear structure used in the DEPFET device of Type-II and IV is plotted in Figure 3.6. It can be seen that the current increases

Figure 3.6: Static characteristic of the punch-through clear structure.

exponentially for voltage values above a threshold voltage of about 3V. The dynamic resistance plotted in Figure 3.6 has similar values as in the case of the punch-through structure.

## 3.3 Depletion characteristics of the DEPFET substrate

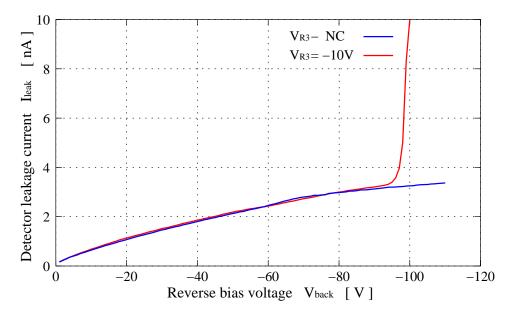

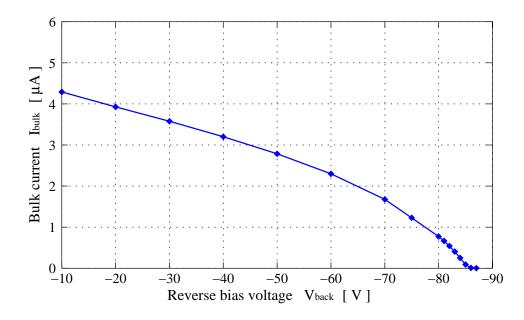

With the detector substrate connected to ground and all the other nodes left floating, a reverse voltage is applied to the back contact ( $p^+$ -implant on the back side) in order to deplete the detector substrate. The leakage current of the depleted substrate is measured versus the applied voltage and is plotted in Figure 3.7 (blue curve). If a  $p^+$  guard ring

Figure 3.7: Detector leakage current.

(e.g. R3) on the top side is connected to a fixed potential (e.g. -10V), a  $p^+ - n - p^+$  punchthrough structure is created between the  $p^+$  guard ring, the *n*-substrate and the  $p^+$  region on the back side. For reverse voltage values larger than the reach-through voltage of the structure, the current increases exponentially with the voltage (the red curve in Figure 3.7). Care must be therefore taken that the voltage difference between the  $p^+$  guard rings on the top side and the  $p^+$  region on the back side of the DEPFET is lower than the reach-through value. This is found to be  $\approx -85V$ .

An indirect method of determining the value of the reverse voltage at which the entire substrate is depleted, is to measure the resistance between two  $n^+$  substrate contacts on the top side as a function of the applied reverse voltage. When the reverse voltage approaches the value that is needed for full depletion, the resistance between the substrate contacts increases very strong with the voltage. Applying a small voltage between the contacts, the current which flows between them decreases to zero at full depletion.

Figure 3.8 shows the current between two substrate contacts (with a voltage difference of 0.2 V) measured as a function of the reverse voltage applied on the back side. It can be seen that the current decreases to zero at a depletion voltage value of  $\approx -86V$  at which the substrate is fully depleted.

In the later operation of the DEPFET, the guard rings are also connected to negative

Figure 3.8: Substrate current versus the reverse bias voltage.

voltages. Since the detector substrate is depleted from both sides, the value of the reverse voltage necessary to deplete the whole substrate is actually smaller than the value determined here (recall the sideward depletion scheme).

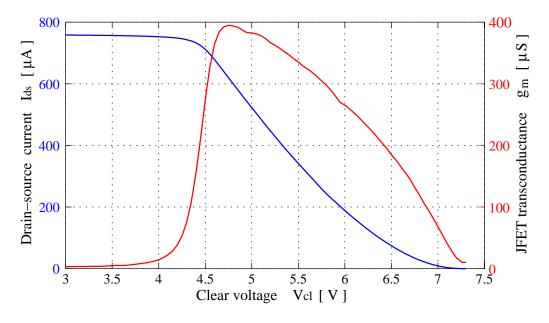

## **3.4** JFET characteristics with the substrate depleted

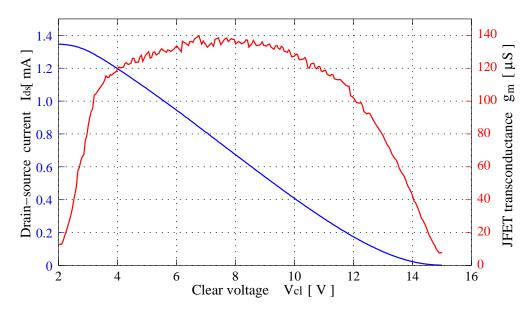

The static characteristics of the JFET transistors were measured again with the detector substrate depleted. The external gate of the JFET is left unconnected and the internal gate voltage is controlled via the clear structure. The depletion voltage on the back side is set to  $V_{back} = -80V$ , the guard rings potentials are set to  $V_{R1} = -10V$ ,  $V_{R2} = -17V$ and  $V_{R3} = -25V$  and the substrate contacts outside the guard rings are set to ground. With the transistor in saturation ( $V_{ds} = -3V$ ), the drain-source current is measured as a function of the applied clear voltage. The  $I_{ds}$ - $V_{cl}$  characteristics of the DEPFET Type-I is shown in Figure 3.9 (the blue curve). One can see that the JFET current remains almost unchanged as far as the clear voltage is lower than the reach-though voltage of the punch-through clear structure. Beyond this value, the internal gate potential varies in the same way as the clear potential and the JFET current decreases with the increasing clear voltage.

The JFET transconductance  $g_m$  determined from the current-voltage curve as  $g_m = \partial I_{ds}/\partial V_{cl}$  is also plotted in Figure 3.9 (the red curve). The values of the transconductance are similar to ones obtained when the JFET is measured with the detector substrate undepleted (compare with Figure 3.2).

Figure 3.9:  $I_{ds}$ - $V_{cl}$  characteristics of the DEPFET Type-I.

The same characteristics measured for the DEPFET Type-III (same clear structure, but different JFET) are plotted in Figure 3.10. The curves are similar to the ones

Figure 3.10:  $I_{ds}$ - $V_{cl}$  characteristics of the DEPFET Type-III.

measured for the DEPFET Type-I, except that the JFET maximum current has larger values. Consequently, the JFET transconductance parameter is also larger.

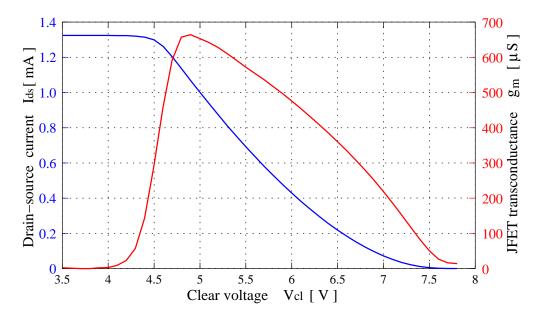

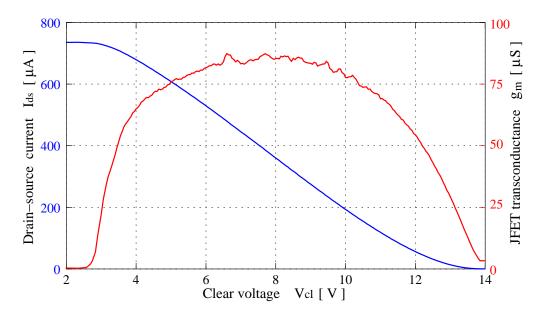

Figure 3.11 shows the  $I_{ds}$ - $V_{cl}$  characteristics of the DEPFET Type-II (same JFET as DEPFET Type-I, but with MOSFET clear structure). It can be seen that the JFET

Figure 3.11:  $I_{ds}$ - $V_{cl}$  characteristics of the DEPFET Type-II.

current decreases with the clear voltage for values larger than the threshold voltage of the MOSFET clear structure. In comparison to the previous DEPFET type, the voltage value at which the channel is pinched off (i.e. JFET current is zero) is much larger. Consequently, the JFET transconductance (the red curve) has lower values at similar current values.

The same characteristics measured for the last DEPFET type are shown in Figure 3.12. They show similarities with the DEPFET Type-II (also with MOSFET clear structure).

Figure 3.12:  $I_{ds}$ - $V_{cl}$  characteristics of the DEPFET Type-IV.

## Chapter 4

# Small-signal and noise analysis of the DEPFET

The analytical analysis of the small-signal equivalent circuit of the continuous clear DEPFET device is performed in this chapter. The noise behavior of the device is also treated here.

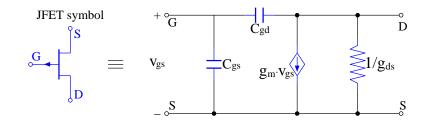

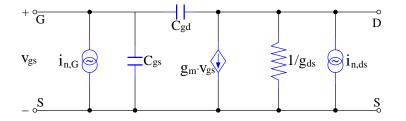

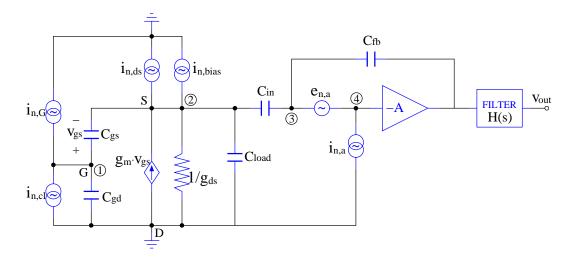

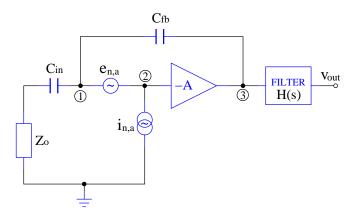

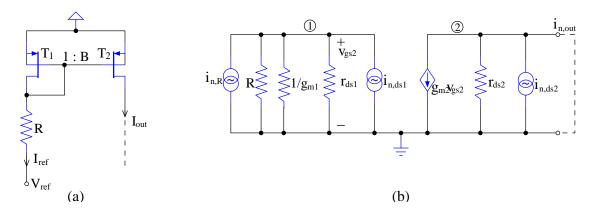

## 4.1 Small-signal equivalent circuit of a JFET

Since the central element of the DEPFET detector is the JFET transistor, the small-signal equivalent circuit model of a JFET is briefly described in this section. The small-signal signal equivalent circuit model is used to described the behavior of any active device (e.g. JFET or MOSFET), when the device is biased to operate at a certain point on its static characteristic and a small AC signal is superimposed on the DC bias values.

Figure 4.1 shows a simplified model [Gray84] of the small-signal equivalent circuit of a JFET transistor in saturation. Since the gate-channel junction of the JFET is reverse

Figure 4.1: Small-signal equivalent circuit of a *p*-channel JFET.

biased, the gate is connected to source and drain only through the equivalent capacitances  $C_{gs}$  and  $C_{gd}$  of the gate-source and gate-drain depletion regions. The JFET channel is represented in the model by a voltage-controlled current source with the current flowing from drain to source. The current value is given by  $i_{ds} = g_m v_{gs}$ , where  $v_{gs}$  is the small AC voltage applied between gate and source and  $g_m$  is the JFET transconductance. The

output impedance  $r_o = 1/g_{ds}$  (see equation 2.16) appears also in parallel to the current source.

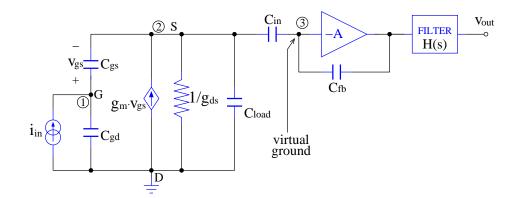

## 4.2 Small-signal analysis of the DEPFET device

One can imagine two principial methods to read out the signal from a DEPFET device. In one of them, the drain-source voltage is kept at a constant value. The charge signal arriving at the internal gate produces a change in the drain-source current which can be further amplified by a current-voltage converter.

In the other method, only the drain node is kept to a fixed potential and a constant current (provided by a current source) flows into the JFET channel at the source. The signal charge in the internal gate causes a potential change at the gate. Since the drainsource current is constant, a similar voltage change takes place at the JFET source. This voltage change is then amplified and processed by appropriate electronics. Operated in this scheme, the JFET is said to be in a *source-follower* configuration (the source "follows" any voltage change at the gate).

The source-follower configuration has several advantages over the configuration with fixed drain-source voltage (also called *grounded-source* configuration). The signal rise time is smaller (i.e. readout can be faster), variations in the pinch-off voltage of the JFET transistor (operating within a DEPFET matrix) have no influence on the signal amplitude; the DEPFET can be DC decoupled from the subsequent electronics.

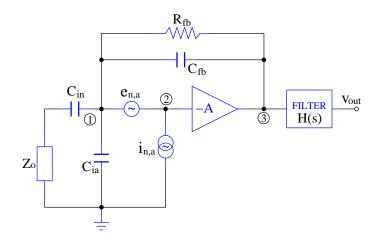

#### 4.2.1 Source-follower configuration of the DEPFET

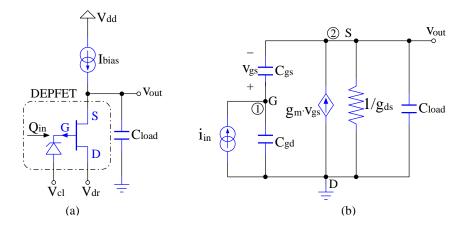

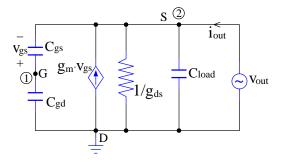

Figure 4.2a shows the electrical circuit in which the DEPFET is in the source-follower configuration. The DEPFET symbol is derived from that of a *p*-channel JFET transistor;

Figure 4.2: Small-signal equivalent circuit of a *p*-channel JFET.

the clear mechanism is represented by a diode due to the analogy of the clear characteristic to that of a forward biased diode. The JFET channel current is provided by a constant current source  $I_{bias}$ . A load capacitance  $C_{load}$  is added at the output node to account for

the parasitic capacitances of the output node and the input capacitance of the subsequent readout stage.

The equivalent small-signal circuit is drawn in Figure 4.2b. The input quantity the signal charge  $Q_{in}$  - is represented by a current source with variable current  $i_{in}(t) = dQ_{in}/dt$ . Since the small-signal analysis is performed in the s-domain (Laplace transform of the time domain),  $i_{in}(s) = sQ_{in}(s)$ .

The voltage-charge transfer characteristic of the circuit is determined by applying Kirchoff's theorem for currents in the circuit nodes 1 and 2:

Node 1:

$$-i_{in} + v_g s C_{gd} + (v_g - v_s) s C_{gs} = 0$$

Node 2:  $g_m(v_g - v_s) - v_s(g_{ds} + s C_{load}) + (v_g - v_s) s C_{gs} = 0$

(4.1)

Eliminating  $v_g$  from both equations and noting that  $v_s = v_{out}$  and  $i_{in} = sQ_{in}$ , one obtains the voltage-charge transfer function:

$$A_{v-q}(s) = \frac{v_{out}}{Q_{in}} = \frac{1}{C_{gd}} \cdot \frac{1}{1 + \frac{g_{ds}}{g_m} \left(1 + \frac{C_{gs}}{C_{gd}}\right)} \cdot \frac{1 + \frac{s}{z_o}}{1 + \frac{s}{p_o}}$$

(4.2)

$z_o$  and  $p_o$  are called *zero* and the *pole* [Sed98] of the transfer function and have the expressions:

$$z_o = \frac{g_m}{C_{gs}}$$

$$p_o = \frac{g_{ds} + g_m \frac{C_{gd}}{C_{gs} + C_{gd}}}{C_{load} + \frac{C_{gd}C_{gs}}{C_{gd} + C_{gs}}}$$

(4.3)

The transfer function  $A_{v-q}$  can be re-written as:

$$A_{v-q}(s) = G \cdot \frac{1 + \frac{s}{z_o}}{1 + \frac{s}{p_o}}$$

(4.4)

where G is the low-frequency gain given by:

$$G = A_{v-q}(0) = \frac{1}{C_{gd}} \cdot \frac{1}{1 + \frac{g_{ds}}{g_m} \left(1 + \frac{C_{gs}}{C_{gd}}\right)}$$

(4.5)

Since  $g_{ds} \ll g_m$  for a JFET in saturation, the gain factor can be approximated as:

$$G \approx \frac{1}{C_{gd}} \tag{4.6}$$

The above equation tells us that the gate-drain capacitance must be minimized in order to have large gain. Assuming a capacitance value of  $C_{gd} = 10 fF$ , the gain factor is  $G \approx 10^{14} V/C = 16 \mu V/e^{-1}$ .

To study the effect of  $p_o$  and  $z_o$  in the transfer function, consider a numerical example for the DEPFET parameters:

$$C_{gs} = 100 \text{fF}$$

$$C_{gd} = 10 \text{fF}$$

$$g_m = 100 \mu S$$

$$g_{ds} = 1 \mu S$$

The values of  $z_o$  and  $p_o$  are then:

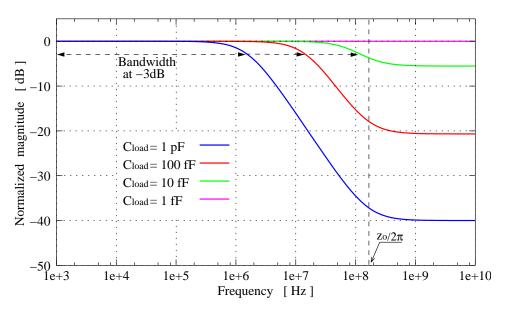

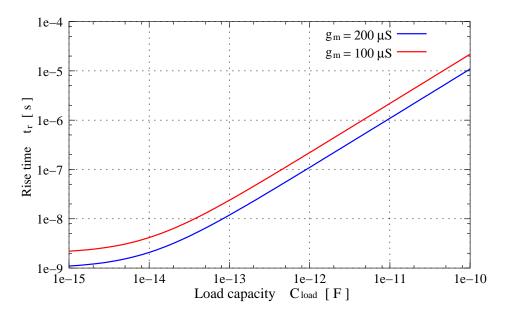

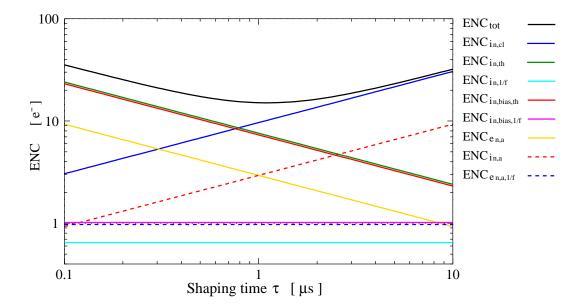

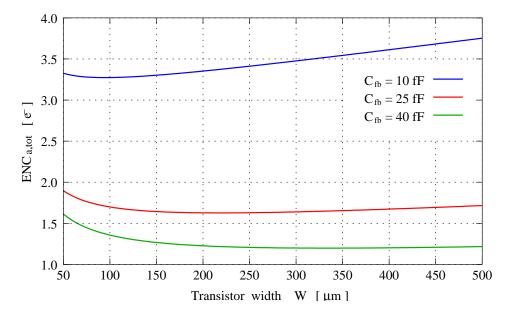

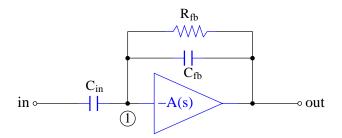

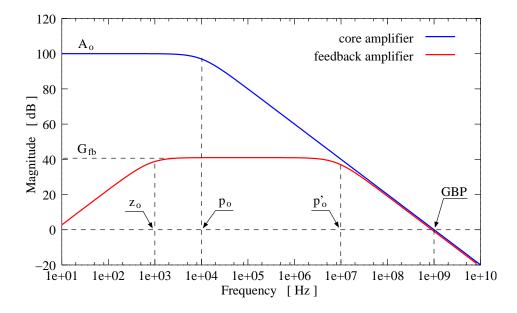

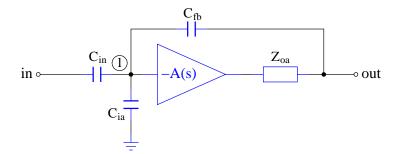

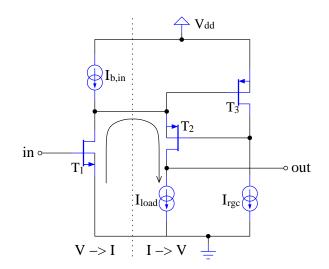

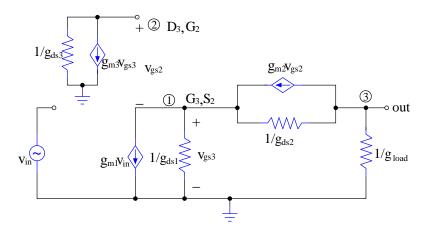

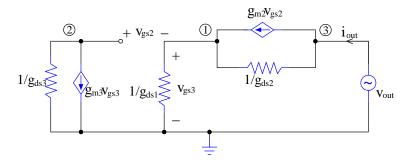

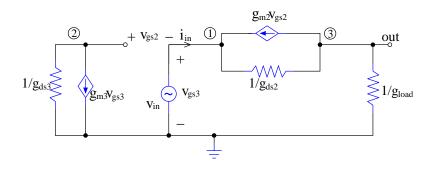

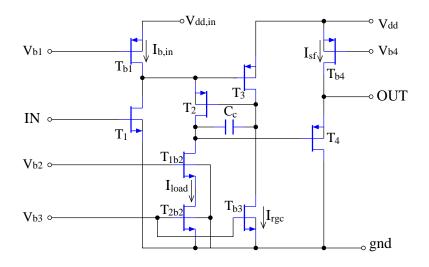

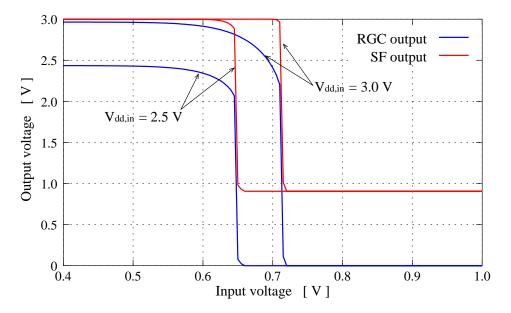

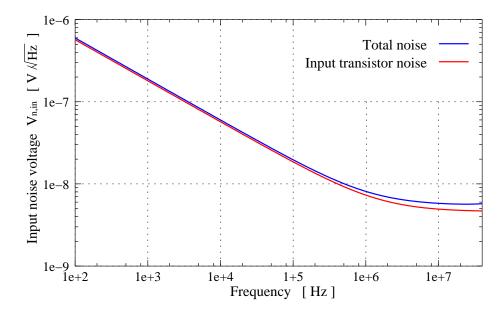

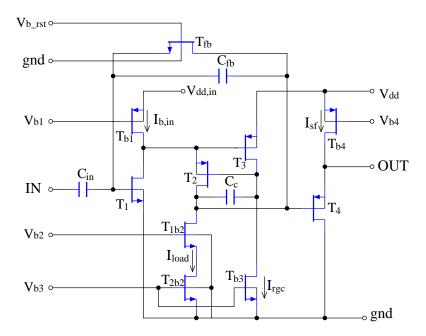

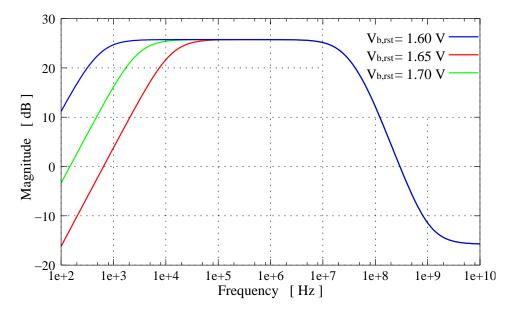

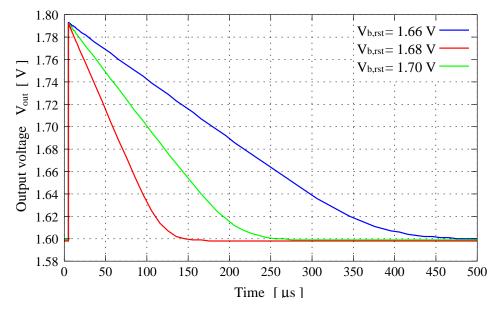

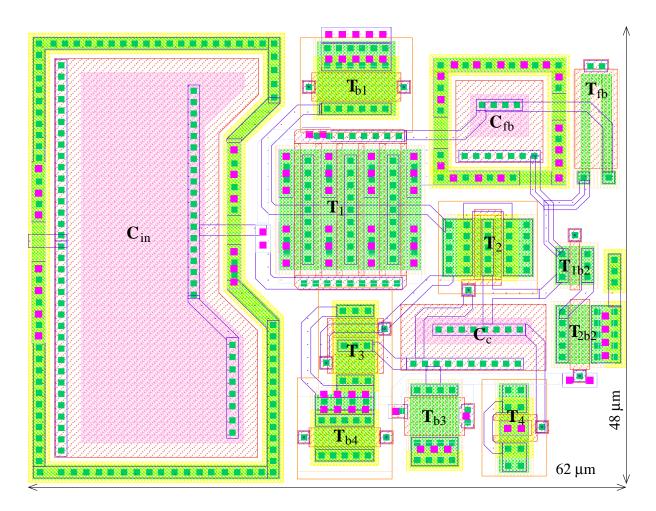

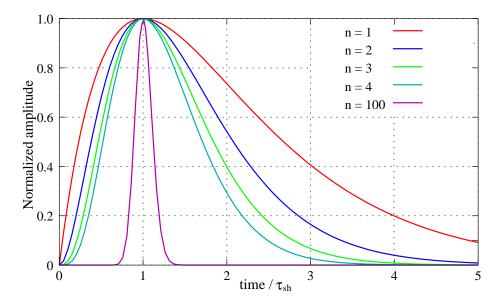

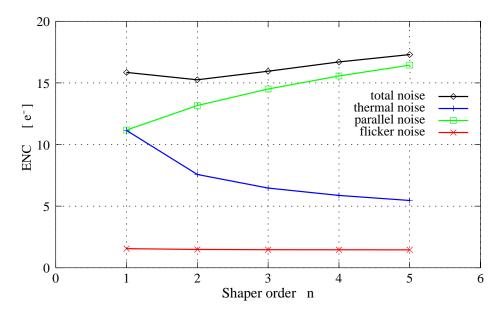

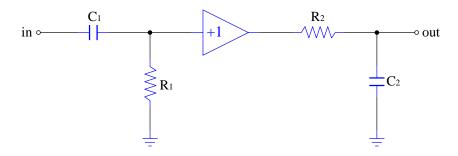

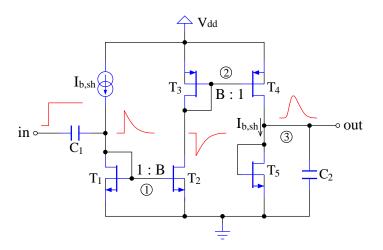

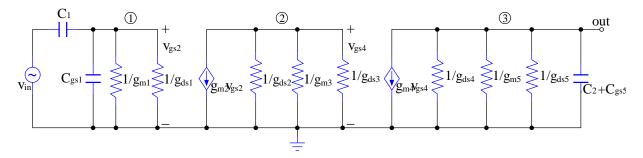

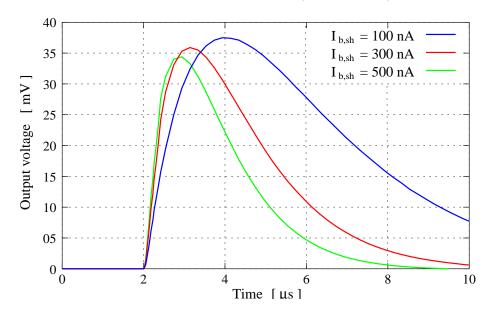

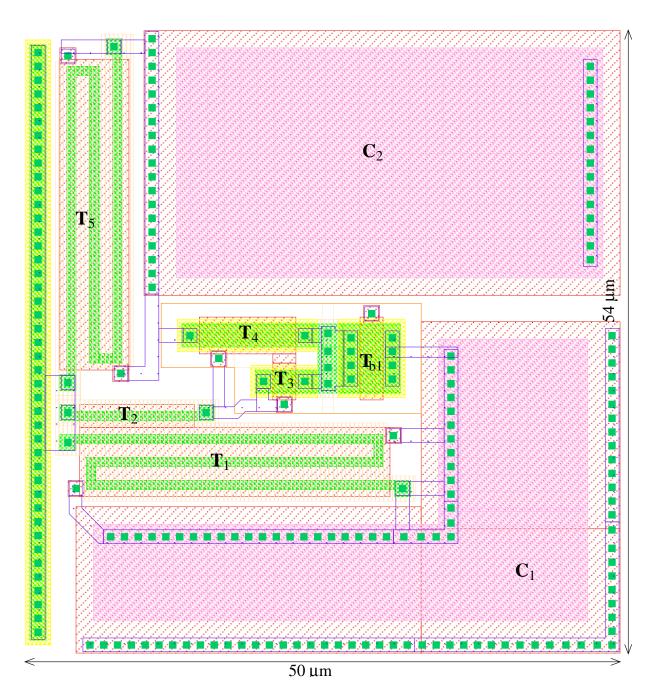

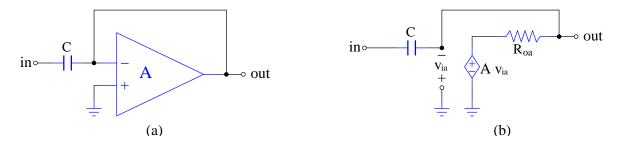

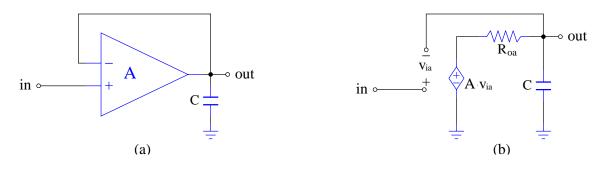

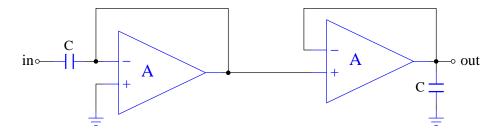

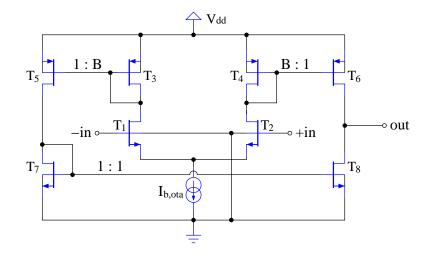

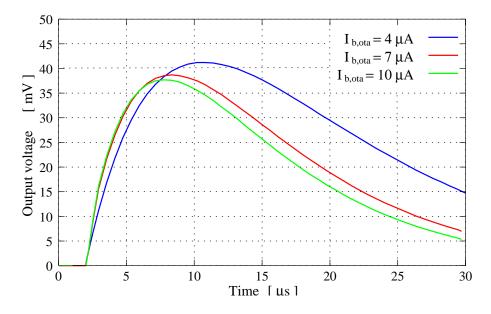

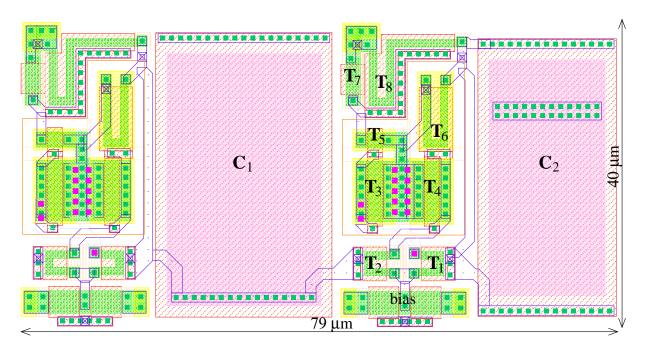

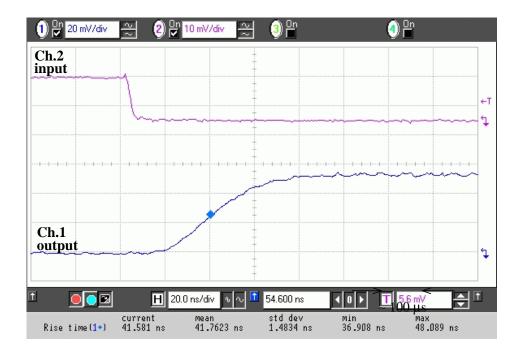

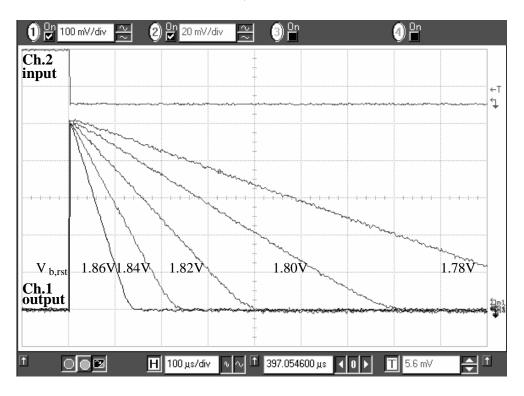

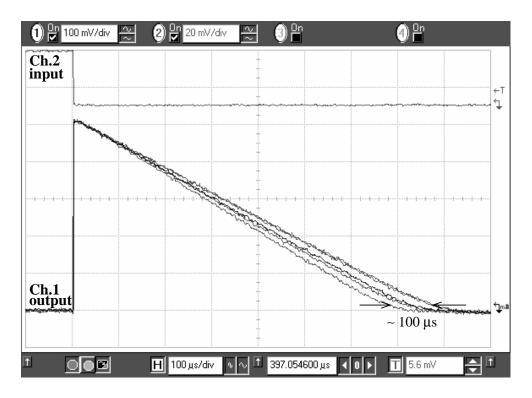

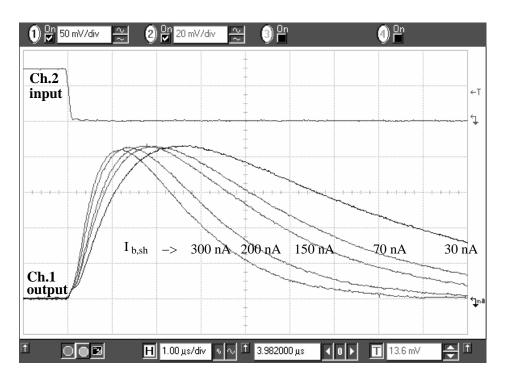

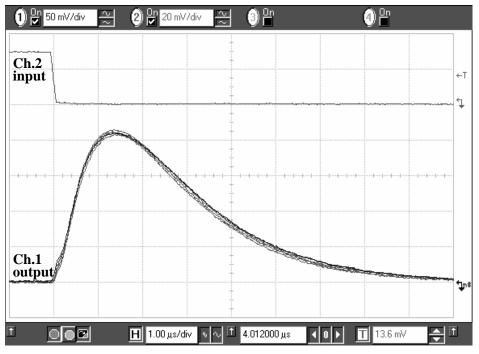

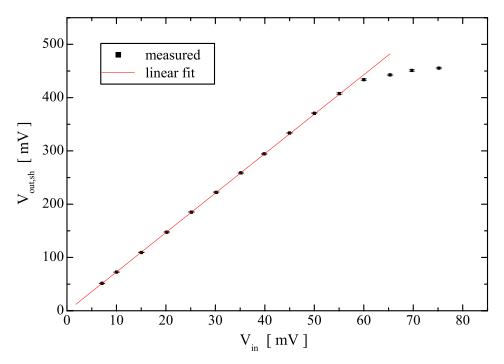

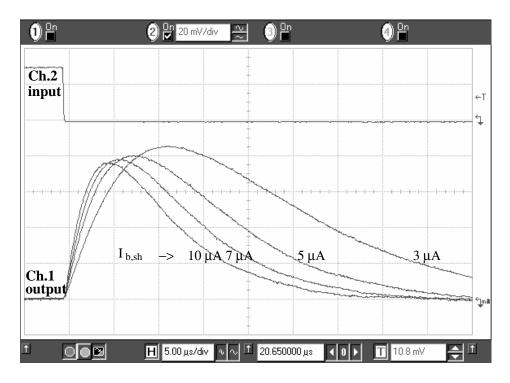

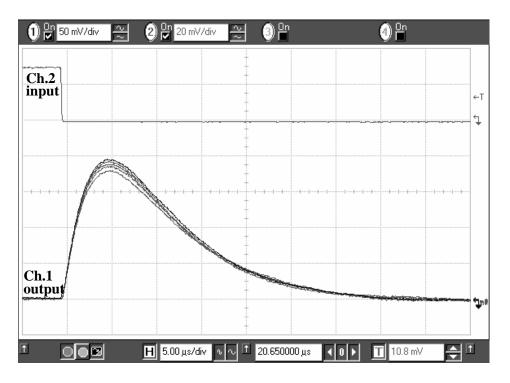

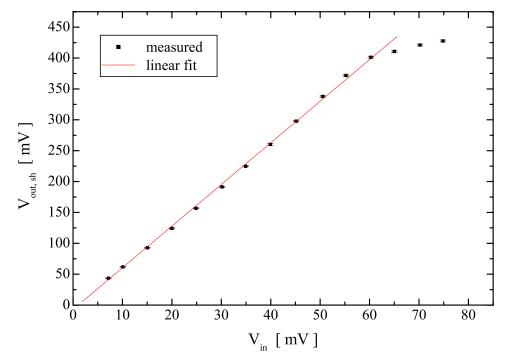

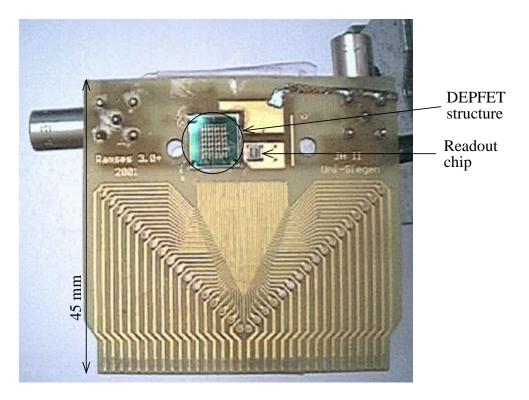

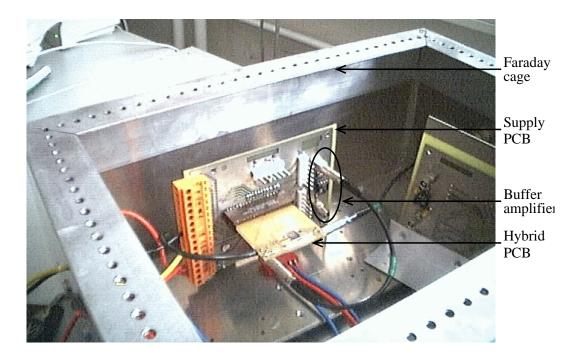

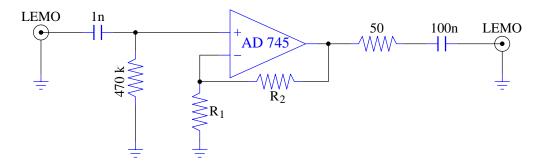

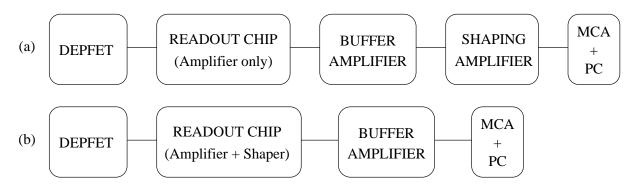

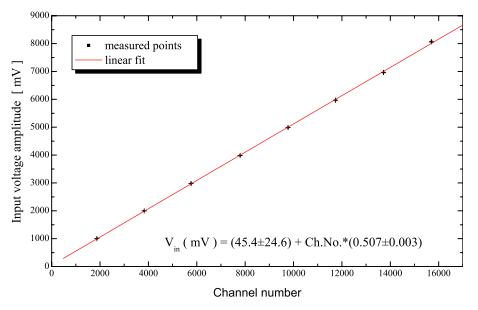

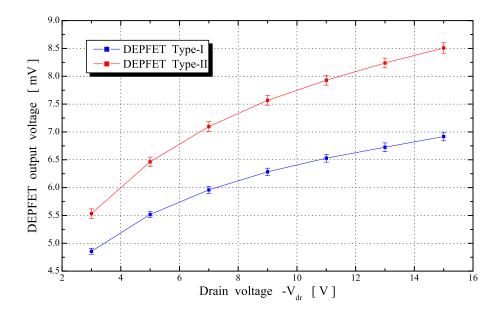

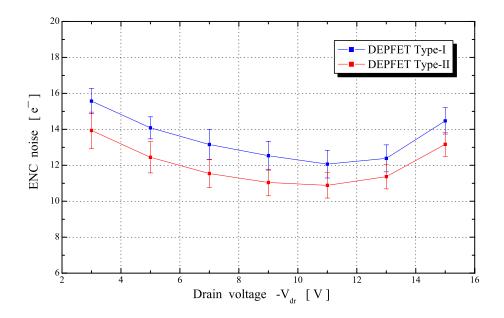

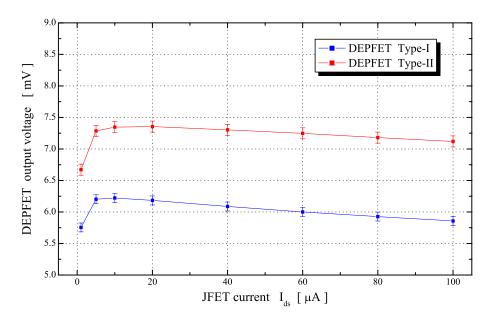

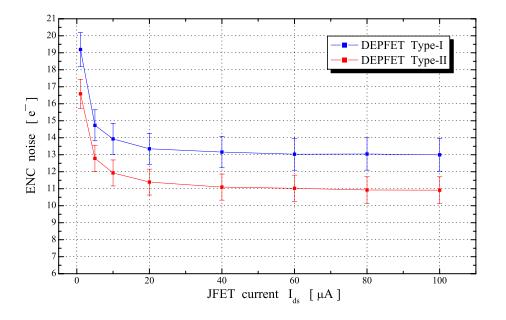

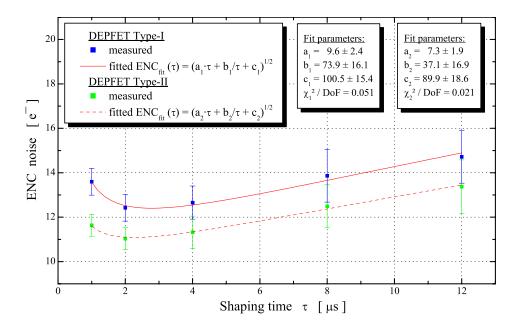

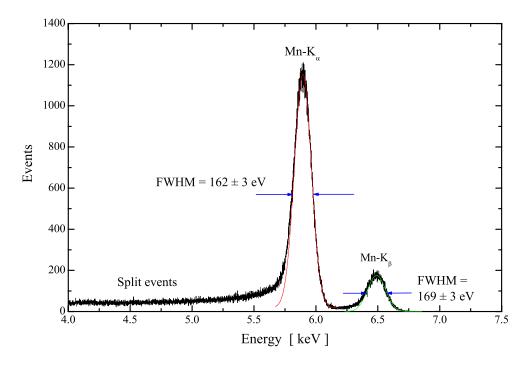

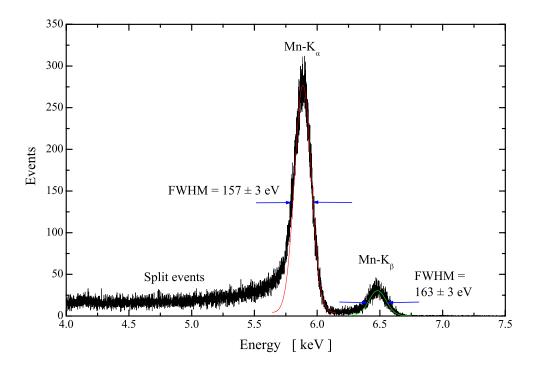

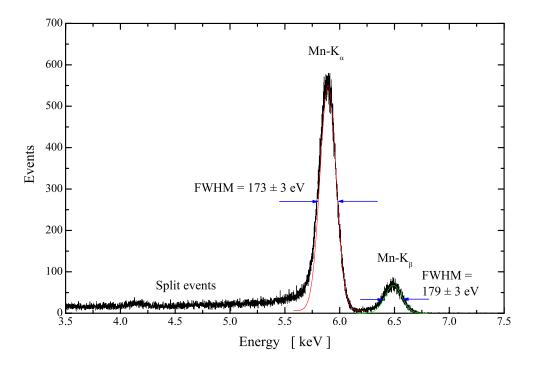

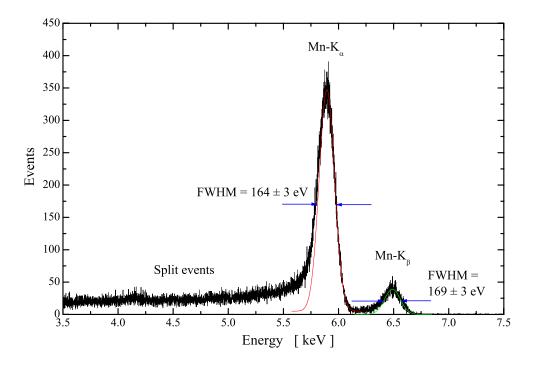

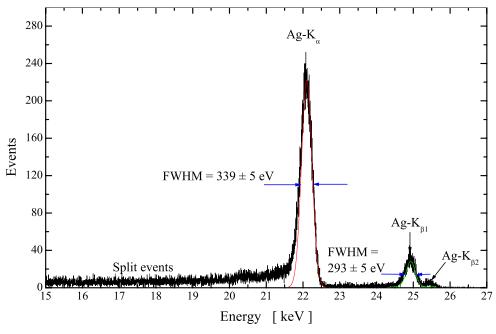

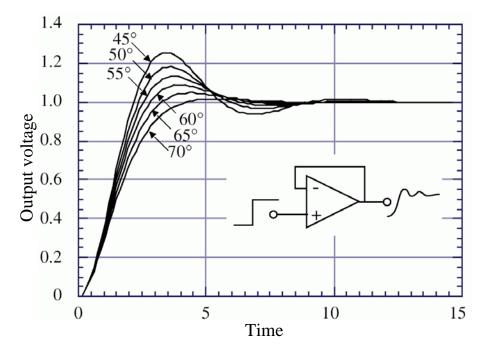

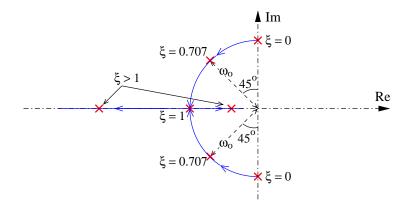

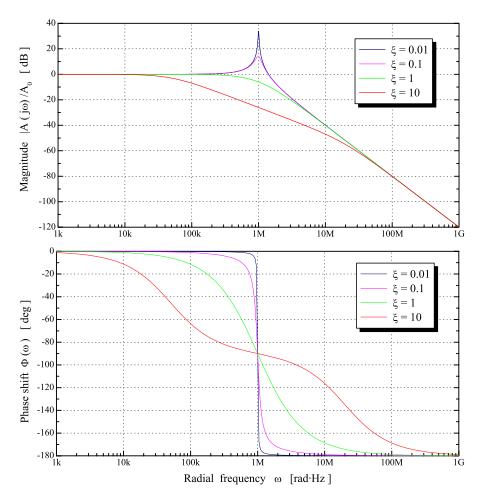

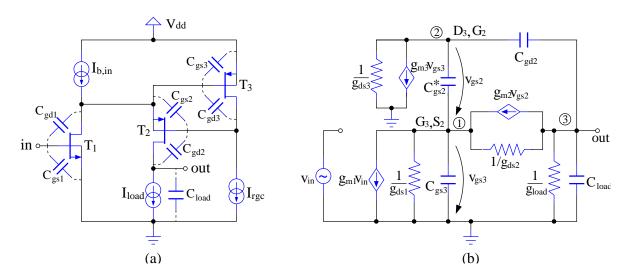

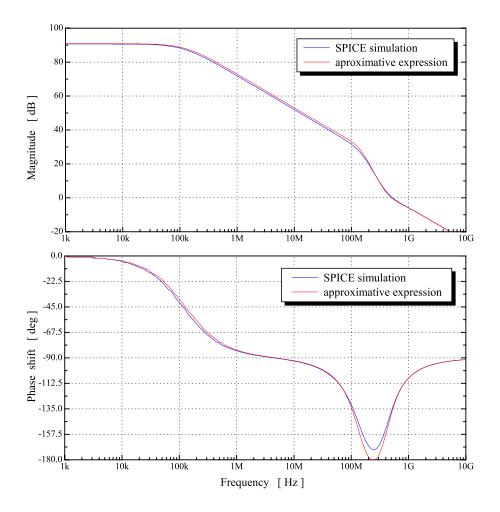

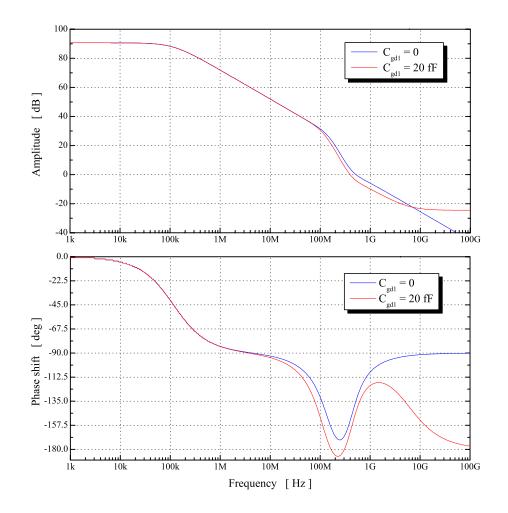

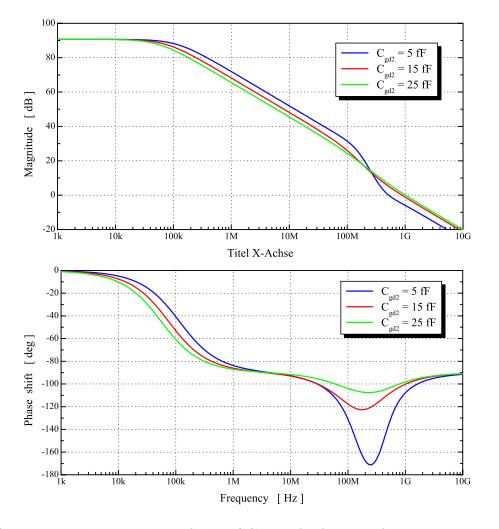

$$z_{o} = \frac{g_{m}}{C_{gs}} = 1GHz$$